Share on 😏 Twitter

in LinkedIn 🛛 🖂 Email

# Simplifying Design of Analog Input Modules for Process Control

## **Cathal Casey**

Applications Engineer, Analog Devices, Inc.

#### Introduction

When designing analog input modules for process control applications such as programmable logic controller (PLC) or distributed control system (DCS) modules, the main trade-off considered is usually performance vs. cost. A tradition exists in this application space of using bipolar  $\pm 15$  V rails to supply active front-end components that are used to attenuate or gain input signals. This impacts the cost of bill of materials (BOM), as well as adding to the complexity of the design with the creation of the isolated bipolar supplies. To save on costs, an alternative approach is to architect with a single 5 V supply. The single 5 V rail greatly reduces the complexity of the design of the isolated supply for the analog front ends. However, it can introduce other pain points and may result in a lower accuracy measurement solution. The AD4111 takes on a lot of the integration needed for voltage and current measurements, and addresses the limitations of a 5 V supply solution.

#### Integrated Front End

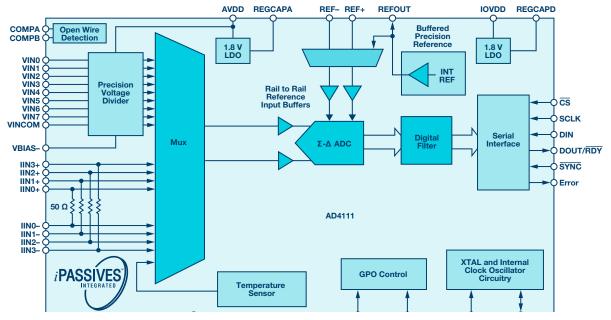

The AD4111 is a 24-bit  $\Sigma$ - $\Delta$  ADC that reduces both development time and the cost of the design by implementing an innovative yet simple signal chain. Utilizing ADI's proprietary *i*Passives<sup>™</sup> technology, it incorporates an analog front end and ADC. This enables the AD4111 to accept ±10 V voltage inputs and 0 mA to 20 mA current inputs while operating off a single 5 V or 3.3 V supply without the need for external components. Voltage inputs are specified to an overrange of ±20 V at which the part will still provide a valid conversion and an absolute maximum specification of ±50 V on a voltage pin. Current inputs are specified to a range of -0.5 mA to 24 mA, which enables accurate current measurements close to 0 mA and provides precise conversions to 24 mA. The voltage inputs of the AD4111 have a guaranteed minimum of 1 M $\Omega$  impedance. This enables the removal of ±15 V external buffers, further reducing board space and BOM costs. 5 V designs are limited by the requirement to have a high impedance voltage divider per voltage input, which uses more board space. The design of a discrete solution becomes a trade-off between cost and accuracy of precision resistors. To resolve this, AD4111 incorporates a high impedance, precision voltage divider per input as shown in Figure 3.

Facebook

Figure 1. AD4111 functional block diagram.

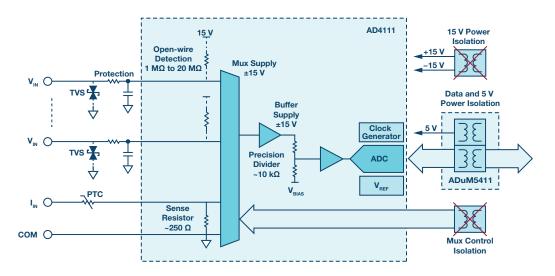

Figure 2. Typical high-end solution.

#### **Open Wire Detection**

Typically, a limitation of single 5 V designs is a lack of open wire detection, which is usually implemented using a high impedance resistor to the 15 V supply rail to pull an open connection to an out-of-range voltage. This is overcome by the AD4111, which boasts the unique capability of open wire detection using a 5 V or 3.3 V supply. This separates open wire detection from an out-of-range fault, further simplifying diagnostics. By including this feature internally on the AD4111, the need for a pull-up resistor on the front end is removed, and thus the need for the 15 V supply reduces the complexity, area, and emissions of the isolation circuitry. For applications where open wire detection is not desired, an alternative generic, the AD4112, is available. This part has all the benefits of the AD4111 but without open wire detection.

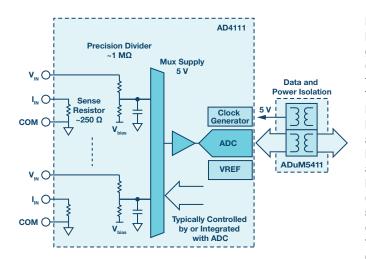

Figure 3. Typical low-end solution.

## System-Level Solution

The AD4111's integration of a voltage reference and internal clock help to reduce board size and BOM cost further, while allowing external components to be used if and when a higher precision and lower error conversion over temperature is required. Figure 2 and Figure 3 show typical high-end and low-end solutions, respectively. Highlighted in both Figure 2 and Figure 3 are the proportions of the signal chain that can be entirely replaced by the AD4111. The AD4111's total unadjusted error (TUE) accuracy specifications were targeted to reach system level requirements. For many solutions, the accuracy may be sufficient to remove the need for any additional calibration. In existing high accuracy solutions, modules are often calibrated per channel. The AD4111 has been designed with highly matched inputs so that calibrating one input will provide a similar level of accuracy across all inputs.

#### EMC Testing

PLC and DCS modules often operate in harsh industrial environments and have to survive electromagnetic interference (EMI) conditions. This adds a greater level of complexity when designing an electromagnetic compatibility (EMC) capable input module since most devices are not rated for EMC, therefore designing the input protection and filtering circuitry becomes complex. This can add significant time to development in terms of design and testing. EMC labs are expensive to rent and failed testing can mean long delays until boards can be redesigned and retested. The AD4111 has been designed into a printed circuit board (PCB) that demonstrates a proven EMC solution. The board is characterized to ensure the circuit performance is not permanently affected by radiated radio frequency (RF) or conducted RF disturbances, and has been shown to have sufficient immunity against electrostatic discharge (ESD), electrical fast transient (EFT), and surge as per the IEC 61000-4-x set of standards. It has also been evaluated for CISPR 11, where the radiated emissions for the board are well below the Class A limits. More information on the AD4111 EMC PCB can be found from AN-1572. This application note details all the necessary information on test procedures used, as well as board design schematics and layout to design an EMC proven input module for the AD4111.

## Conclusion

The AD4111 is a system-level ADC with high levels of integration, which includes a comprehensive degree of configurability. Its ability to take  $\pm 10$  V voltage inputs and 0 mA to 20 mA current inputs, and operate from a single 5 V or 3.3 V supply with open wire detection, along with its many other features, provides a unique solution for analog input module design. It comes in a 6 mm  $\times$  6 mm, 40-lead LFCSP and enables modules that once required a full complex PCB to now be replaced by a single device.

For more information on any of the above mentioned products, visit *analog.com/ADC*.

## About the Author

Cathal Casey is an applications engineer with the Precision Converter Technology Group at Analog Devices in Cork, Ireland. His main focus is on precision  $\Sigma$ - $\Delta$  ADCs for dc measurements He joined Analog Devices in 2016 after graduating from University College Cork. He holds a bachelor's degree in electrical and electronic engineering. He can be reached at *cathal.casey@analog.com*.

## Online Support Community

Engage with the Analog Devices technology experts in our online support community. Ask your tough design questions, browse FAQs, or join a conversation.

Visit ez.analog.com

#### Analog Devices, Inc. Worldwide Headquarters

Analog Devices, Inc. One Technology Way P.O. Box 9106 Norwood, MA 02062-9106 U.S.A. Tel: 781.329.4700 (800.262.5643, U.S.A. only) Fax: 781.461.3113

#### Analog Devices, Inc. Europe Headquarters

Analog Devices GmbH Otl-Aicher-Str. 60-64 80807 München Germany Tel: 49.89.76903.0 Fax: 49.89.76903.157

#### Analog Devices, Inc. Japan Headquarters

Analog Devices, KK New Pier Takeshiba South Tower Building 1-16-1 Kaigan, Minato-ku, Tokyo, 105-6891 Japan Tel: 813.5402.8200 Fax: 813.5402.1064

#### Analog Devices, Inc. Asia Pacific Headquarters

Analog Devices 5F, Sandhill Plaza 2290 Zuchongzhi Road Zhangjiang Hi-Tech Park Pudong New District Shanghai, China 201203 Tel: 86.21.2320.8000 Fax: 86.21.2320.8222 ©2019 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. Ahead of What's Possible is a trademark of Analog Devices. DN21111-0-3/19

#### analog.com