Con la continua migración de la industria a cosas como el comercio electrónico, el trabajo remoto y la computación en nube, las demandas de los centros de datos siguen creciendo exponencialmente.

La DRAM estándar DDR4 ha tenido una adopción generalizada desde 2014. Sin embargo, el aumento de la demanda de confiabilidad, disponibilidad y estado de funcionamiento por parte de los clientes en los últimos años ha hecho evidente que se necesita una nueva generación de DRAM. Recientemente, Micron Technology, Inc. anunció un amplio Programa de habilitación tecnológica (TEP) para ayudar en el diseño, el desarrollo y la calificación de las plataformas de computación de próxima generación que utilizan DRAM DDR5, la más avanzada disponible en la actualidad.

En enero de 2020, Micron anunció el lanzamiento de muestras de RDIMM DDR5. En julio de 2020, JEDEC (la Organización mundial de estándares para la industria electrónica) publicó su muy anticipado estándar SDRAM DDR5 JESD79-5. Debido a su experiencia con los tecnicismos de la nueva DRAM y su compromiso con los nuevos estándares, empresas como Micron, Cadence, Montage, Rambus, Renesas y Synopsys existen en el nexo de las demandas del mercado y el desarrollo técnico. Con el TEP, este grupo de empresas trabajará mano a mano con socios comerciales como distribuidores, revendedores de valor agregado y OEM a medida que desarrollan productos nuevos con esta nueva tecnología.

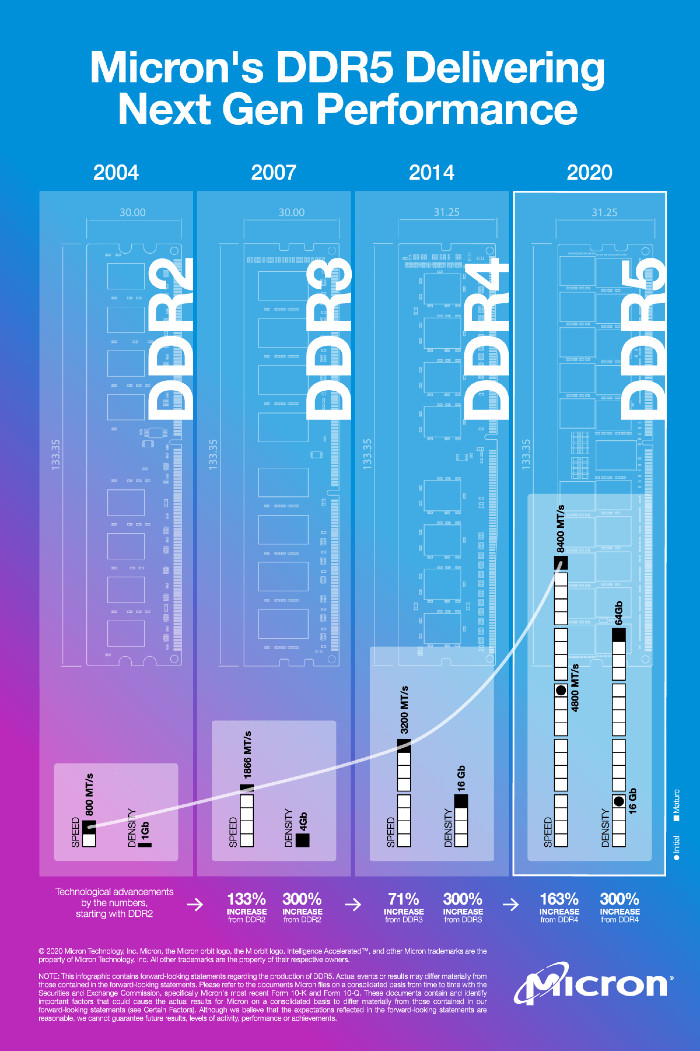

DDR5 es el DRAM más avanzada a nivel tecnológico hasta la fecha. Fabricada a partir de la tecnología de procesos de 1 znm líder en la industria de Micron, la DDR5 ofrece un aumento de más del 85 % en el rendimiento de la memoria. La clave de este avance es la densidad de la memoria: la DDR5 tiene el doble de su predecesor DDR4. En esta infografía, vea cómo la DRAM ha experimentado aumentos exponenciales de velocidad con el tiempo, y cómo la DDR5 es la mejor hasta ahora.

Esta evolución en la velocidad permite el aumento del ancho de banda de la memoria y la capacidad necesarias para alimentar centros de datos de vanguardia con un número de núcleos de procesador en rápida expansión. La siguiente tabla ofrece una visión general de las ventajas de la DDR5:

| Característica/Opinión | DDR4 | DDR5 | Ventaja de la DDR5 | |||

| Tasas de transferencia de datos | 1600 a 3200 MT/s | 3200 a 6400 MT/s | Aumenta el rendimiento y el ancho de banda | |||

| VDD/VDDQ/VPP | 1.2/1.2/2.5 | 1.1/1.1/1.8 | Baja la potencia | |||

| VREF interno | VREFDQ | VREFDQ, VREFCA, VREFCS | Mejora los márgenes de tensión, reduce los costos de la lista de materiales | |||

| Densidades de los dispositivos | 2 Gb a 16 Gb | 8 Gb a 64 Gb | Admite dispositivos monolíticos más grandes | |||

| Precarga | 8 n | 16 n | Mantiene el reloj interno del núcleo bajo | |||

| Ecualización del receptor DQ | CTLE | DFE | Mejora la apertura de los ojos de los datos DQ recibidos dentro de la DRAM | |||

| Ajuste del ciclo de trabajo (DCA) | Ninguno | DQS y DQ | Mejora la señalización en los pines de DQ/DQS transmitidos | |||

| Retardo interno de DQS Monitoreo |

Ninguno | Oscilador de intervalos de DQS | Aumenta la robustez frente a los cambios ambientales | |||

| ECC en matriz | Ninguno | SEC 128 b + 8 b, comprobación de errores y depuración | Refuerza el RAS en el chip | |||

| CRC | Lectura | Lectura/escritura | Fortalece el sistema RAS mediante la protección de los datos leídos | |||

| Grupos de bancos (BG)/bancos | 4 BG x 4 bancos (x4/x8) 2 BG x 4 bancos (x16) |

8 BG x 2 bancos (8 Gb x4/x8) 4 BG x 2 bancos (8 Gb x16) 8 BG x 4 bancos (16 a 64 Gb x4/x8) 4 BG x 4 bancos (16 a 64 Gb x16) |

Mejora el ancho de banda/rendimiento | |||

| Interfaz de comando/dirección | ODT, CKE, ACT, RAS, CAS, WE, A |

CA<13:0> | Reduce de manera significativa el número de pines de CA | |||

| ODT | DQ, DQS, DM/DBI | DQ, DQS, DM, bus de CA | Mejora la integridad de la señal, reduce los costos de la lista de materiales | |||

| Longitud del estallido | BL8 (y BL4) | BL16, BL32 (y BC8 OTF, BL32 OTF) |

Permite la obtención de una línea de caché de 64 B con solo un subcanal de DIMM. | |||

| MIR (pin “mirror”) | Ninguno | Sí | Mejora la señalización de DIMM | |||

| Inversión del bus | Inversión del bus de datos (DBI) | Inversión de comando/dirección (CAI) | Reduce el ruido de VDDQ en los módulos | |||

| Capacitación de CA, capacitación de CS | Ninguno | Capacitación de CA, capacitación de CS | Mejora el margen de tiempo en los pines CA y CS | |||

| Modos de capacitación de nivelación de escritura | Sí | Mejorado | Compensa la incomparable trayectoria de DQ-DQS | |||

| Patrones de capacitación de lectura | Es posible que con el MPR | MR dedicadas para la serie (definido por el usuario), el reloj y la LFSR -patrones de capacitación generados |

Hace que el margen de tiempo de lectura sea más robusto | |||

| Registros de modos | 7 x 17 bits | Hasta 256 x 8 bits (tipo de lectura/escritura LPDDR) |

Proporciona espacio para expandirse | |||

| Comandos de PRECARGA | Todo el banco y por banco | Todo el banco, por banco y el mismo banco | El PREsb permite la precarga de un banco específico en cada BG | |||

| Comandos de ACTUALIZACIÓN | Todo el banco | Todo el banco y el mismo banco | El PREsb permite la actualización de un banco específico en cada BG | |||

| Modo loopback | Ninguno | Sí | Permite probar la señalización de DQ y DQS |

Beneficios del Programa de compromiso técnico DDR5 de Micron (TEP):

Los socios aprobados pueden tener acceso a:

- Recursos técnicos como hojas de datos, modelos eléctricos, térmicos y de simulación para ayudar en el desarrollo de productos y la puesta en marcha de plataformas.

- Seleccionar muestras de componentes y módulos de DDR5 a medida que estén disponibles.

- Conexión con otros socios del ecosistema que pueden ayudar en el diseño y la puesta en marcha de plataformas habilitadas de DDR5.

- Apoyo técnico y material de capacitación.

Descargar el comunicado de prensa