# Stratix 10 FPGA Board with 16GB HBM2

Powerful solution for accelerating memory-bound applications

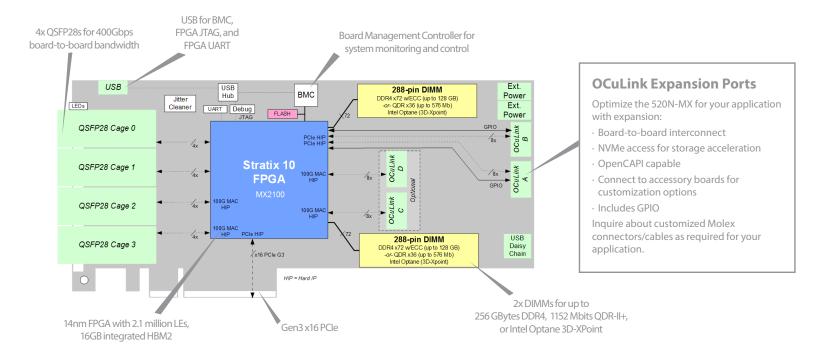

Designed for compute acceleration, the 520N-MX is a PCIe board featuring Intel's Stratix 10 MX2100 FPGA with integrated HBM2 memory. The size and speed of HBM2 (16GB at up to 512GB/s) enables acceleration of memory-bound applications. The board's 100G QSFP28s are ideal for clustering, and OCuLink connectors allow expansion.

Both traditional HDL and higher abstraction C, C++ and OpenCL-based tool flows are supported. Deliverables include an optimized board support package (BSP) for the Intel OpenCL SDK.

The 520N-MX features a Board Management Controller (BMC) for advanced system monitoring and control, which greatly simplifies platform integration and management.

## Tool Flow Flexibility for Softwareor Hardware-Based Development

- OpenCL support for softwareorientated customers

- $\cdot \ Abstration for faster development$

- Push-button flow for FPGA executable, driver, and API

- Add optimized HDL IP cores to OpenCL designs as libraries

- Traditional VHDL/Verilog support for hardware-orientated customers

- · Hand-code for ultimate performance

- · High-Level Synthesis (HLS) available for rapid development

- · FPGA card designed to support standard Intel IP cores for Stratix 10

key features

Intel Stratix 10 MX2100

16GB HBM2 up to **512GB/s**  OpenCL BSP

# **Additional Services**

Take advantage of BittWare's range of design, integration, and support options

#### **Customization**

Additional specification options or accessory boards to meet your exact needs.

#### **Server Integration**

Available pre-integrated in our <u>TeraBox servers</u> in a range of configurations.

### **Application Optimization**

Ask about our services to help you port, optimize, and benchmark your application.

#### **Service and Support**

BittWare Developer Site provides online documentation and issue tracking.

### **Board Specifications**

| •                                 |                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FPGA                              | Intel Stratix 10 MX     MX2100 in an F2597 package     16GBytes on-chip High Bandwidth Memory (HBM2) DRAM, 410 GB/s (speed grade 2)     Core speed grade -2: I/O speed grade -2     Contact BittWare for other Stratix 10 MX options                                                                                                     |

| On-board Flash                    | 2Gbit Flash memory for booting FPGA                                                                                                                                                                                                                                                                                                      |

| External memory                   | <ul> <li>2x 288-pin DIMM slots each fitted with 16GB modules by default, i.e., 32GB total on board (options up to 256GB total)</li> <li>Contact BittWare for QDR-II+ &amp; Intel Optane (3D-Xpoint) DIMM options</li> </ul>                                                                                                              |

| Host interface                    | x16 Gen3 interface direct to FPGA, connected to<br>PCle hard IP                                                                                                                                                                                                                                                                          |

| QSFP cages                        | <ul> <li>4 QSFP28 cages on front panel connected directly to FPGA via 16 transceivers</li> <li>User programmable low jitter clocking supporting 10/25/40/100GbE</li> <li>Each QSFP28 can be independently clocked</li> <li>Jitter cleaner for network recovered clocking</li> <li>2 QSFP28s have available 100GbE MAC hard IP</li> </ul> |

| OCuLink                           | <ul> <li>2x edge connectors (A, B) @ 12.5G per lane (default); each supports PCle Gen 3 x8 hard IP, GPIO, and PCle master and optional input clocking</li> <li>2x inner connectors (C, D) @ 25G per lane (optional); OpenCAPI capable, 1x 100GbE MAC hard IP per OCuLink</li> </ul>                                                      |

| Board<br>Management<br>Controller | <ul> <li>Voltage, current, temperature monitoring</li> <li>Power sequencing and reset</li> <li>Field upgrades</li> <li>FPGA configuration and control</li> <li>Clock configuration</li> <li>Low bandwidth BMC-FPGA comms with SPI link</li> <li>USB 2.0</li> <li>PLDM support</li> <li>Voltage overrides</li> </ul>                      |

| Cooling       | <ul> <li>Standard: double-width active heatsink (with fan)</li> <li>Optional: double-width passive heatsink</li> <li>Optional: double-width liquid cooling</li> </ul>                                             |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Electrical    | <ul> <li>On-board power derived from 12V PCle slot &amp; two<br/>AUX connectors (one 8-pin, one 6-pin)</li> <li>Power dissipation is application dependent</li> <li>Typical max power consumption 225W</li> </ul> |

| Environmental | Operating temperature: 5°C to 35°C                                                                                                                                                                                |

| Quality       | <ul> <li>Manufactured to ISO9001:2015 IPC-A-610-Class III</li> <li>RoHS compliant</li> <li>CE, FCC &amp; ICES approvals</li> </ul>                                                                                |

| Form factor   | <ul> <li>Standard-height PCle dual-slot board</li> <li>4.376 x 10.5 inches (111 x 266.7 mm)</li> </ul>                                                                                                            |

### **Development Tools**

| FPGA<br>development     | BIST - Built-In Self-Test for CentOS 7 provided with source code (pinout, gateware, PCle driver & host test application)               |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Application development | Supported design flows - Intel FPGA OpenCL SDK,<br>Intel High-Level Systesis (C/C++) & Quartus Prime Pro<br>(HDL, Verilog, VHDL, etc.) |

#### **Deliverables**

- 520N-MX FPGA board

- USB cable (front panel access)

- Built-In Self-Test (BIST)

- OpenCL HPC Board Support Package (BSP)

- 1-year access to online Developer Site

- 1-year hardware warranty

# To learn more, visit www.BittWare.com

Rev 2019.04.23 | April 2019

© BittWare 2019

Stratix 10 is a registered trademark of Intel Corp. All other products are the trademarks or registered trademarks of their respective holders.