今日のコンピュータでは、揮発性および不揮発性の内部ストレージ ユニットが多種多様に利用されています。ダイナミックランダムアクセスメモリ (DRAM) は、コスト効率に優れているため、最も頻繁に採用されるアーキテクチャの1つです。 静的ランダムアクセスメモリ (SRAM)。この記事では、同期ダイナミック アクセス メモリ (SDRAM) を含むさまざまな種類のDRAMと、さまざまな種類のダブル データ レート (DDR) トポロジ (DDR2、DDR3、DDR4など) 間の主な違いについて簡単に説明します。

DRAMとは何ですか?

一般的に ディーラムと発音されるダイナミック ランダム アクセス メモリ (DRAM) は、ランダム アクセス メモリ (RAM) の個々のビットを保存するための一連の コンデンサ を実装します。RAMは、シーケンス内の位置に関係なくデータ要素にアクセスできるメモリの一種です。したがって、本質的には、データにアクセスするのにかかる時間は一定です。アクセス トランジスタとストレージ、コンデンサの最適な設計、および半導体プロセスの進歩により、DRAMストレージは最も安価なメモリになりました。前述のように、DRAMはSRAMに比べてコスト効率に優れているため、コンピューターのメイン メモリとして最もよく使用されます。DRAMテクノロジは、数十年にわたって大幅な改訂が行われ、ビットあたりのコストが大幅に削減され、クロック レートが向上し、このコンポーネントの全体的な寸法が縮小されました。これらの改善は、より小型のDRAMセル、同期DRAMアーキテクチャ、そして最終的にはDDRトポロジの導入など、さまざまな変更に関連しています。

DRAMセル構造

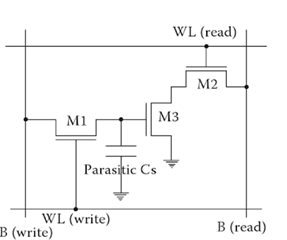

一般的な3トランジスタDRAMセルでは、 アクセス トランジスタ と ストレージ トランジスタ を使用して、ストレージ トランジスタの入力容量をオン (ビット値1) とオフ (ビット値0) に切り替えます。トランジスタのアレイは、読み取りと書き込みの 列ライン と 行ライン に接続されており、これらはそれぞれ ビットライン と ワードライン とも呼ばれます。コンポーネントとデータ ラインは、単一のストレージ トランジスタで書き込み操作と読み取り操作の両方を実行できるように配置されています。

たとえば、従来の3トランジスタDRAMセル (図1) は、M1アクセス トランジスタのゲートに電圧を送信して書き込みコマンドを実行し、M3のゲート容量を充電します。次に書き込みラインが低く駆動され、M3のゲート容量に蓄積された電荷がゆっくりと消散します (これがダイナミックという用語の由来です)。

図1: 3トランジスタDRAMセル (左) と1トランジスタ/1コンデンサDRAMセル (右)。

[画像提供: ダイナミックRAM: テクノロジーの進歩]

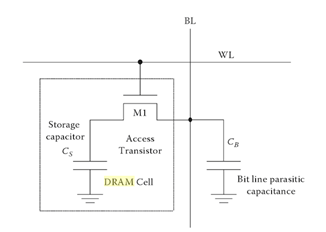

現在の技術では、より高密度に詰め込まれたメモリ チップに1トランジスタ/1コンデンサ (1T1C) メモリ セル (図1) が採用されることが多いです。CMOSゲートはワード ラインに接続され、ソースはビット ラインに接続されます。書き込みコマンドは、トランジスタのゲートをオンにして個別のストレージ コンデンサに電流を送ることによって実行されます。読み取りは、コンデンサに蓄積された電荷をビット ラインと共有することによって実行されます。このアーキテクチャでは、電荷共有によってDRAMセルに含まれる情報が破壊されるため、読み取り操作のたびに再書き込み (リフレッシュ) が必要になります。通常、この再充電は、コンデンサからの電荷漏れを補うために数ミリ秒ごとに行われます。

非同期転送モード (ATS) スイッチング

このテクノロジーの本当の複雑さは、書き込み、読み取り、更新などのさまざまな操作について、数千個のセルの配列を追跡および評価する必要がある階層のいくつかのレイヤーにあります。現在のDRAMテクノロジでは、行アドレスと列アドレスの両方に同じアドレス入力ピンが活用される 多重化アドレス指定 が利用されており、これにより最終的にスペースが節約され、ピン数が削減されます。

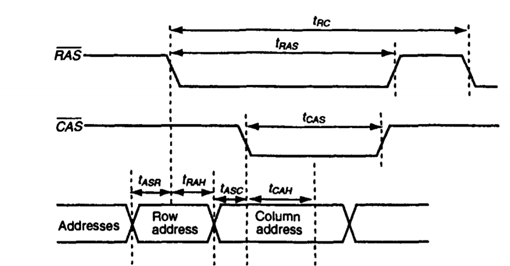

行アドレス ストローブ (RAS) と列アクセス ストローブ (CAS) クロックを使用して実行される操作。RASはDRAMに送信された信号が実際に行アドレスであることを検証し、CASは入力列アドレスを検証します。RASの立ち下がりエッジで、DRAMアドレス ピンにあるアドレスが行アドレス ラッチに入力されます。CASの立ち下がりエッジで、アドレスが列アドレス ラッチに入力されます。本質的には、メモリ アレイ内の行全体をオンにすると、コンデンサに保存されている情報を読み取る (感知する) ことができるようになり、または書き込みのためにストレージ コンデンサを充電/放電できるようになります。

これは、行/列ラッチ、行アドレス バッファ、行/列デコーダ、ワードライン ドライバ、ビットライン センス アンプなどの多数の周辺回路を使用することで実現されます。1T1C DRAMセルの場合、読み取られたDRAMセルの情報の損失を防ぐために、 センス アンプ が行バッファとしてよく使用されます (読み取られるたびに、そのDRAMセルの情報が破壊されます)。センス アンプは基本的に、ストレージ コンデンサに十分な電荷があるかどうかを感知し、低電力信号を取得して完全なロジック値 (0または1) に増幅します。情報がロードされ、センス アンプに格納されるまで、メモリ内の選択された行にはアクセスできません。これにより、 CAS レイテンシが発生し、必要な行が要求された時点でアクティブになっていない場合、追加の時間が必要になります。

図に示すように 図2最初のステップでは、 RA 電圧が低い場合、行全体のすべてのセルがセンス アンプによって読み取られますが、このプロセスには比較的長い時間がかかります。この後、行はアクティブになり、列にアクセスして読み取りまたは書き込みを行うことができます。アクセス時間(読み取り/書き込みサイクル時間)は RA 一般的には CAS センス増幅ステップによるものです。非同期DRAMのバス速度は通常66 MHzを超えません。

図2: 非同期DRAMのアドレス タイミング。

[画像提供: DRAM回路設計: チュートリアル]

SDRAMとDRAM

DRAMは同期モードまたは非同期モードのいずれかで動作します。同期モードでは、すべての操作 (読み取り、書き込み、更新) がシステム クロックによって制御されます。このシステム クロックは、コンピューターのCPUのクロック速度 (約133 MHz) と同期しています。その理由は、従来のDRAMよりもはるかに高いクロック速度 (3倍) を実現できるためです。DRAMとの間のすべての操作は、マスター クロックの立ち上がりエッジで実行されます。一般的なシングル データ レート (SDR) SDRAMクロック レートは100 MHzと133 MHzです。

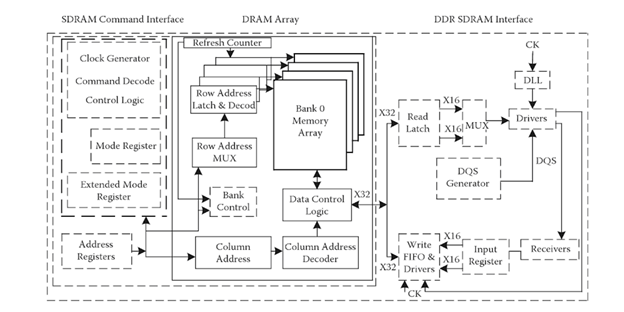

SDRAMアーキテクチャにおける大きな差別化要因の1つは、メモリが同じサイズの複数のセクションに分割されていることです。これらの記憶 銀行 アクセス コマンドを同時に実行できるため、平均的なDRAMよりもはるかに高速な速度を実現できます。図に示すように 図3 DRAMの基本的なコアと動作は本質的に同じですが、同期インターリーブにはDRAMチップとは別にI/Oコマンド インターフェイスが含まれます。

SDRAMの高速化に大きく貢献したのは、 パイプライン-- 1つのバンクがプリチャージ状態にあり、アクセス待ち時間が発生している間に、別のバンクで読み取りが行われ、メモリ チップが継続的にデータを出力している可能性があります。つまり、複数のバンクのアーキテクチャにより、異なる行への同時アクセスが可能になります。

SDRAMとDDR

シングル データ レート (SDR) SDRAM (単にSDRAMと呼ばれることが多い) のクロック レートは多くのアプリケーションには十分ですが、マルチメディア アプリケーションには十分ではないことがよくあります。SDRAMの次のバージョンは、ダブルデータレートSDRAM (DDR SDRAM) でした。主な進化は、すべてのコマンドと操作がクロックの立ち上がりエッジでのみ実行され、マスター クロックの立ち上がりエッジと立ち下がりエッジの両方でデータを転送する機能によってもたらされました。つまり、クロック サイクルごとに2倍のデータが送信されることになります。

これは、 プリフェッチ ワイド内部バスが2ビット(ワード)のデータを同時にプリフェッチする操作。 バースト 等幅の2つのワードがI/Oピンに出力されます。2ビット プリフェッチとも呼ばれるこの方式は、メモリ ユニットの電力消費量を増やすことなく、データ レートを本質的に2倍にします。また、DDRアーキテクチャでは電力効率が著しく向上していることにも注目すべきです。DDR2は2.5V、DDR3は1.5V ~ 1.65V、DDR4は1.2Vで動作します。これは、デバイスの電源管理回路の改訂と、消費電力を増やすことなくデータ転送の頻度をよりスマートに増やす機能によるものです。消費電力の削減により、DDRモジュールは、バッテリー電源で動作するコンピューター (ラップトップなど) にとってより望ましい選択肢になります。

DDR、DDR2、DDR3、DDR4 - 違いは何ですか?

DDRのその後の進化(DD2、DD3、DDR4)の基礎となるコンポーネントと機能/操作は同じままですが、差別化要因はメモリ容量の増加です。 クロック速度。たとえば、DDR2 RAMはDDR SDRAMインターフェイスに2倍のクロック乗算器を追加し、同じバス速度を維持しながらデータ転送速度を2倍にします。このようにして、メモリ アレイからI/Oバッファへの「4ビット プリフェッチ」が使用されます。同様に、DDR3モジュールでは8ビットのデータがプリフェッチされ、DDR4モジュールでは16ビットのデータがプリフェッチされます。

図3: SDRAMインターフェイス (右) とDDR制御インターフェイス (左) を備えたDRAMメモリ アレイ。

[画像提供: ダイナミックRAM: テクノロジーの進歩]

揮発性DRAMアーキテクチャのコアは基本的に同じままですが、オフチップの追加コマンド インターフェイスによって容量が増加し、ビットあたりのコストが削減されました。DRAMのパフォーマンスにおけるこの大きな進化は、データのパイプライン化とI/Oバッファ周波数の増加に貢献する可能性があります。

- Siddiqi、Muzaffer A. ダイナミック ラム: テクノロジーの進歩。CRCプレス、2017年。

- Keeth、Brent、およびR. Jacob Baker。DRAM回路設計: チュートリアル。IEEEプレス、2001年。