很多系统需要时钟输入,某些 RF 应用需要快速、精确地提供一些特定频率。尽管模拟合成技术已经沿用了数十年,但是直接数字合成技术于 20 世纪 70 年代开始流行开来。

锁相环频率控制

所有闭环模拟控制的原理都是一样的,而不论所控制的是马达还是真空管振荡器。有一个设备(被控制对象)、一种指定所需输出条件的输入、一种确定错误(当前的输出偏差)的量度或累积块、以及一个能够调整设备操作以获取所需输出的控制块。在原理图中,控制块常与设备相组合,因为调整控制元件与调节设备输入的联系非常紧密。

锁相环控制跟标准的发电站控制环类似。PLL circuits controlled vacuum tube oscillators, but modern chips are designed for on-board crystal control.所需的频率发生器为压控振荡器 (VCO),很多集成电路将其集成到设备中,仅需要使用一般的无源元件即可运行。MC14046B 是来自安森美半导体的产品,诸如这种设备包含相位比较器、VCO、源极跟随器、保护二极管以及滤波 电路,以产生缓冲输出,后者可作为标准振荡器的输出来使用。

参阅相关产品

对 VCO 的输入取决于外部电阻器 以及设计师所选择的电容器。因此,使用电位器 等可变电阻器可帮助用户控制输出频率。

PLL 控制回路,摘自安美森半导体 MC14046B 数据表

顾名思义,压控振荡器是一种可以根据输入电压来变更频率的振荡器。它们通常使用水晶制成,后者可造成因温度而引发的频移或高抖动。控制回路本身受模拟部件的速度的支配,对某些设计来说可能速度不够快。可合成频率的范围和粒度对现代系统而说可能不够用,尤其是通讯领域的系统更是如此。

直接模拟合成:理论与现实

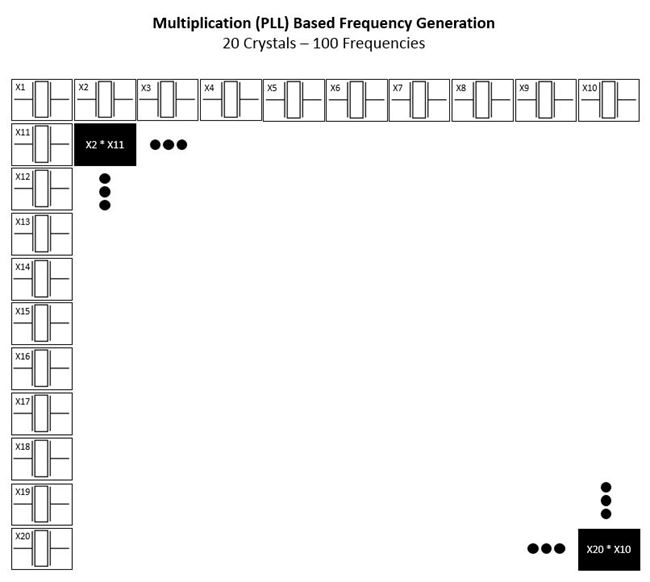

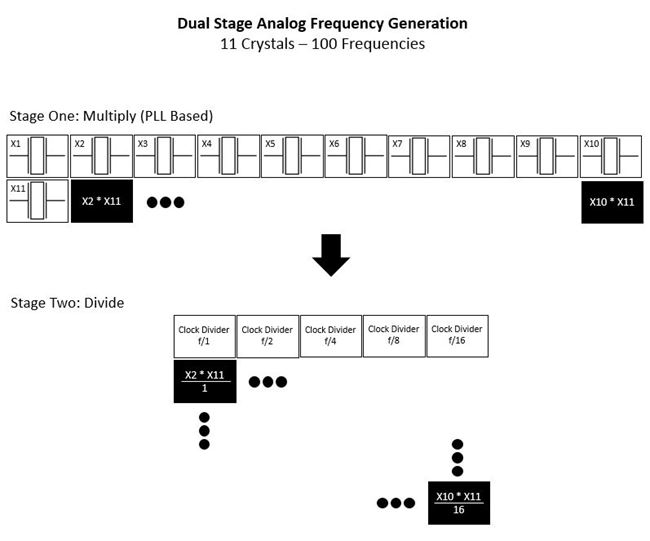

基于锁相环路频率控制的常见合成架构有两种。锁相环路可允许您对两种频率进行相乘,从而获得一个新的频率,这种新的频率不是任一初始频率的直接谐波。这就意味着,您只需运用乘法运算即可获得 20 个时钟源,而无需借助于 100 种晶体来获得 100 个非谐波频率。实际上这会动用 20 多个相位比较器集成电路来获得真正的动态频率捷变,但相比使用 100 种晶体,其物料成本和占用的电路板空间会双双下降。

这种只借助乘法的技术被称为乘法滤波器或混合滤波器架构。更为复杂的版本称为混合/乘法-混合-分频架构,该架构同时用到乘法技术和时钟分频器。

时钟可使用标准逻辑进行二等分、四等分等操作,并且还有一些集成电路可供您动态地选择分频等级。这些集成电路通常还可提供相位匹配和缓冲,以使输出信号的直接作用最大化。

参阅相关产品

尽管模拟合成技术在理论上无懈可击,但在实施过程中的诸多挑战激励行业不断寻找更好的解决方案。相比于开关振荡器,混合滤波器设计是更好的替代方案,这是因为其使用更少的振荡器,却能维持相位记忆,相位记忆是指允许振荡器维持初始输出频率相位的一种特性。在使用混合-滤波器-分频架构时,这种特性常会受损。并非所有应用都需要精准的相位匹配,但在诸多合成的频率“问题”中,ø=0 的生成波远低于高精度扫描系统的理想值。

直接数字合成 - 先进性能

直接数字合成属于信号合成的范畴。所有个体组件或组成部分均已出现了很长时间,并且在各种各样的应用当中独立使用,但是不同部件相结合却创造出了一种近乎适用于所有场景的新产品。

尽管相比于模拟合成中的 VCXO,直接数字合成器有时会被称为数控振荡器 (NCO),但严格来讲,称其为“振荡器”是错误的,因为该设备没有任何部件发发生振荡。恰恰相反,数字元器件生成的能够在数模转换器 (DAC) 运行的样本波形,接近于真正的模拟正弦波。

DDS 集成电路需要一种来自处理器 的输入,这种输入叫作“控制字”。控制字的位宽决定了 DDS 能够创建的最大操作步数。这种输入连同一个已知的时钟频率一起进入相位累加器,后者在模拟控制系统中起到错误块的作用,并进行离散数学积分。相位累加器的输出值是二进制的(在某些先进架构中是十进制的)字,进入正弦映射查找表。说白了,查找表不过就是存储在内存中的一个表格,而这个阶段的输出则是一种数字化的正弦波形近似值。随后,样本波形通过 DAC 和外部滤波电路创造出平顺的模拟正弦波形。

相比于模拟合成解决方案,严格意义上的数字元器件可以运行得极为快速和精确,前者往往受限于输入时钟的准确度,而非因累加器或内存造成的限制。但是,DAC 会带来信号衰减等问题,而信号速度是产生有用波形所必需突破的瓶颈。因此,在一个完整的 DDS 中,DAC 是限制性能的典型元器件。Analog Devices 等厂商会借助多重高总线宽度 DAC 等技术来实现高性能。

参阅相关产品

总体来说,凭借更精细的粒度,DDS 可在更广泛的频率范围内提供更高的性能,但它通常也是一种更为昂贵的解决方案,需要对合成有更深刻的理解才能有效地将其集成到设计中去。需要多重频率的慢速系统仍能借助基于锁相环路的模拟合成技术取得成功,但 DDS 技术已经彻底颠覆了高频、高速以及高精度系统获得其生成时钟的方式。

想要了解更多信息?请观看我们的简明概述:何为直接数字合成?