アプリケーションで50Vを超える電圧やわずか数ミリオームのMOSFETが必要な場合、利用できる統合ソリューションはありません。代わりに、ゲート ドライバーを備えたスタンドアロンのMOSFETまたはIGBTを設計する必要があります。

MOSFETは、瞬時にオンとオフを切り替える単純なデバイスではありません。図1に示すように、寄生成分があり、高電力で動作する場合、これが大きな影響を及ぼします。

たとえば、MOSFETのRDsonが低いほど、入力容量は高くなります。数千pF単位の値が一般的です。

MOSFETをオンにするときは、コンデンサを充電する必要があります。コンデンサのサイズに応じて、異なる電流値が使用されます。ほとんどのドライバー ファミリは、500mA、1A、2A、4Aの値に分かれています。Analog Devices, Inc. のポートフォリオは、主に2Aと4Aに重点を置いています。ゲート ピンの目的の電流を微調整するには、抵抗器を直列に配置します。この抵抗器は、一方では電力消費に影響を与え、他方ではEMI効果に影響を与えます。したがって、アプリケーションの設計段階でトレードオフを決定する必要があります。

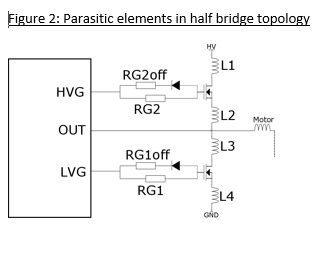

ハーフブリッジは一般的なトポロジですが、出力ピンのグランド以下の電圧と誘導されたターンオン現象という2つの厄介な問題に直面しています。半導体デバイスによる寄生成分に加えて、ボードレイアウトによって、図2のL1、L2、L3、L4に示すような新しい寄生成分が発生します。適切な設計では、これらの寄生要素の影響を制限する必要があります。

誘発ターンオン現象:

MOSFETがオフになると、ミラー寄生容量のために、同じハーフブリッジ上の他のMOSFETがオンになっているときに、誤ってMOSFETがオンになる危険性があります。ミラー寄生容量によってゲートに注入される電流により、MOSFETのゲートに望ましくない電圧の増加が発生します。誘導ゲート電圧は、寄生容量CGS の絶対値、CGD との相対比、ハーフブリッジのdVOUT/dtの値、およびソースとゲート間の等価(ターンオフ)抵抗の値によって決まります。図3はこの現象を示しています。

このリスクを最小限に抑えるには、次の3つのアクションが推奨されます。

- ゲートとソース間の抵抗パスを減らします。ゲートの電圧降下が減少します。

- 最大Vout/dtを減らします。この低減は、ゲート抵抗値を増やすことで実現でき、これによりMOSFETのターンオンのゲート電流が制限されます。この欠点は、スイッチング時間の増加によって整流中に消費される電力が増えることです。

- CGD/CGS比が低いMOSFETを使用します。

OUTピンのグランド電圧以下

Hブリッジのハイサイドがオフの場合、電流はローサイドで再循環します (図4を参照)。遷移中、ダイオードはごく短い時間(数ナノ秒)にわたって全負荷電流を流し始めます。寄生インダクタンスにより、アンダーシュートスパイクが発生します。このアンダーシュートを最小限に抑える最善の戦略は、ハイサイドMOSFETのターンオフを遅くしてdi/dtを減らすことです。寄生インダクタンスを最小限に抑えるには、ボードのレイアウトも非常に重要です。次の2つのレイアウトのヒントが役立ちます:

- インダクタンスと抵抗は、トレース長に正比例し、幅に反比例します。つまり、ドライバとMOSFET間の領域を小さくすることが最善です。ローサイド ドレインとハイサイド ソース間のトレースが可能な限り短く広くなるように、各ハーフブリッジの両方の電源スイッチを可能な限り互いに近づけて配置します。

- インダクタンスフリーのシャント抵抗器を使用します。

これらの実装は通常は十分ですが、電圧スパイクがまだ強すぎると判断される場合は、グランド ピンとOUTピンの間にある高電圧高速ダイオードなどのアクティブ コンポーネントによって、グランド以下の電圧スパイクがクランプされます。

これらのヒントを使用すると、特定のニーズに適合するゲート ドライバーを備えたスタンドアロンMOSFETまたはIGBTを設計できます。

関連商品を見る