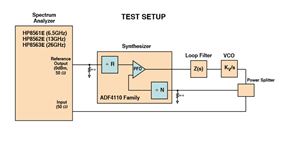

位相ロック ループ (PLL) における位相ノイズとリファレンス スプリアスの原因と、それらを最小限に抑える方法については、 Analog Devices のこの記事で詳しく説明しています。また、位相ノイズと基準スプリアスの測定技術、およびこれらのエラーがシステム全体のパフォーマンスに与える影響についても検討します。最後に、オープンループ変調方式における出力リーク電流の重要性の例を使用して検討します。PLLに関連する重要な仕様についての詳細と図解については、以下をお読みください。

ブラウザを更新してもう一度お試しください。問題が解決しない場合はお問い合わせください

位相ロック ループ (PLL) における位相ノイズとリファレンス スプリアスの原因と、それらを最小限に抑える方法については、 Analog Devices のこの記事で詳しく説明しています。また、位相ノイズと基準スプリアスの測定技術、およびこれらのエラーがシステム全体のパフォーマンスに与える影響についても検討します。最後に、オープンループ変調方式における出力リーク電流の重要性の例を使用して検討します。PLLに関連する重要な仕様についての詳細と図解については、以下をお読みください。

お問い合わせとサポート

注目の製品

業種とトレンド

Our website places cookies on your device to improve your experience and to improve our site. Read more about the cookies we use and how to disable them here. Cookies and tracking technologies may be used for marketing purposes.

By clicking “Accept”, you are consenting to placement of cookies on your device and to our use of tracking technologies. Click “Read More” below for more information and instructions on how to disable cookies and tracking technologies. While acceptance of cookies and tracking technologies is voluntary, disabling them may result in the website not working properly, and certain advertisements may be less relevant to you.

We respect your privacy. Read our privacy policy here