アナログ設計環境の変化の中で、オペアンプと呼ばれるオペアンプは時代遅れという認識が常に覆されてきましたが、オペアンプにおける同相モード除去比 (CMRR) と電源電圧除去比 (PSRR) の重要性が高まっていることは、この目覚ましい技術進化の証です。

オペアンプは、その優れた精度、高い熱ドリフト、そして驚くべき設計の汎用性により、アナログ設計の重要な構成要素です。これは、正極端子と負極端子の2つの入力端子を同じポイントに適用して1つの出力を作成する差動増幅器です。

オペアンプの構造から、その設計における最も重要な2つのパラメータ、CMRRとPSRRがわかります。アナログ設計はより高い帯域幅へと移行しているため、それらの役割は特に重要です。その結果、ノイズや消費電力などの問題がオペアンプのパフォーマンスにおいて重要になります。

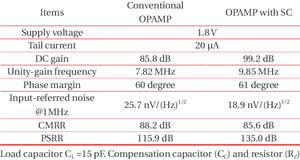

図1: 2段オペアンプ デバイスのシミュレーションされたパフォーマンス。下部にCMRR値とPSRR値が表示されます。(画像出典: Research Gate)

たとえば、オペアンプの役割は、特にセンサーが非常に小さな電圧を生成し、デジタル化する前に信号を増幅する必要がある場合に、電力が制限された組み込みアプリケーションで信号調整を実行するため、 センサー をマイクロコントローラのアナログ/デジタル コンバータ (ADC) 入力にリンクする上で重要になりつつあります。

CMRRやPSRRなどのパラメータの重要性は、ゲインや帯域幅などのオペアンプの機能が温度係数や製造上のばらつきにほとんど依存しないという事実にも関係しています。代わりに、周波数スパイクや電源電圧の変化などの外部要因によって決まります。

この記事では、CMRRおよびPSRRメトリックがオペアンプのパフォーマンスと効率に本質的にどのように関連しているか、また、より優れた消費者向けおよび産業用設計を構築しようとする開発者の取り組みにどのような影響を与えるかについて説明します。また、エンジニアがプロジェクト用のオペアンプを選択する際に慎重に検討する必要がある設計上の推奨事項も紹介します。

ノイズとEMIに対抗するCMRR

同相モード除去比(CMRR)は、オペアンプ製品において最も重要な仕様の1つです。なぜ?これは、オペアンプの入力にコモンモード信号が存在することを示し、最終的にはオーディオ、ビデオ、通信設計におけるノイズを最小限に抑えるオペアンプの能力を決定します。

ここで、CMRRの重要性についてさらに詳しく説明する前に、理想的なシナリオではオペアンプのCMRRは無限大であるはずであることに注目する価値があります。これは、入力信号内のコモンモード要素がオペアンプの入力で同時かつ同位相であるように見える場合、クリーンかつ正確な出力信号を生成するというオペアンプの基本的な前提が無効になるためです。

ただし、実際にはCMRRは無限大にはならず、オペアンプはCMRRが可能な限り高くなるように設計する必要があります。入力側の差動動作モードにより、オペアンプはコモンモード入力 (CMI) を構成するさまざまな周波数成分を除去し、不要なノイズや電磁干渉 (EMI) を抑制できます。これは、オペアンプがCMI要素を減衰できるようにするには、高いCMRRが重要である理由を示しています。

差動入力がオペアンプのCMI信号に匹敵する場合、CMRRはさらに重要になります。オペアンプは入力端子でCMI信号を抑制し、高調波をキャンセルして歪みを低減できる必要があります。

ノイズの多い環境で動作する熱電対の例を考えてみましょう。環境からのノイズによって両方の入力がオフセットされ、コモンモード電圧信号が生成され、必然的にオペアンプの出力電圧に影響を与える可能性があります。

図2: Linear Technologyの LTC 1050 オペアンプの用途には、熱電対やバッテリ駆動の温度モニタなどがあります。(画像提供: Analog Devices Inc.)

最後に、オペアンプのプレイブックの脚注: CMRRとコモンモード除去 (CMR) という用語は同じ意味で使用され、その量はデシベル (dB) で表されます。

CMRR関連設計上の考慮事項

高精度オペアンプには、高精度、広い動作電圧範囲、堅牢な動作が求められます。ここで、これらのオペアンプの機能により、高いCMRRによりトリミングやキャリブレーションの必要がなくなり、広い温度範囲にわたって一貫したパフォーマンスが保証されます。

CMIの発生は主に抵抗値の不均衡が原因であり、CMRRを改善する1つの方法は、入力端子の抵抗値を均衡させることです。さらに、設計条件によっては、入力電圧を変更することで電源とコモンモード範囲に対応できます。

また、差動入力を確実にするために、高インピーダンスの電流ソースまたはシンクを使用し、差動ペアをバイアスするために抵抗器を使用しないことが最善です。これによりゲインが一定に保たれ、CMRR値が高くなります。多くのオペアンプはCMRR値が90 dBにも達すると主張しています。

電源感度を測定するPSRR

大規模から小規模まで電子設計における電力効率の需要の高まりにより、電源電圧変動除去比 (PSRR) は着実に重要性を増しています。これは、入力レベルでどれだけの妨害信号が注入されたかを測定するもので、その結果、調整された出力に影響を与える可能性があります。また、入力レベルでさまざまな周波数要素を除去しながら、オペアンプが電力供給をどれだけうまく実行できるかを示します。

オペアンプのPSRRとは、電源電圧の変化に対する入力オフセット電圧の変化によって入力側に発生するノイズやリップルを除去する能力です。 そのため、車載、産業、医療の設計における厳しい動作条件で安定性を確保する上で、特に設計者が消費電力を最小限に抑えたいバッテリー駆動のデバイスに搭載されるオペアンプにとって、オペアンプは重要な役割を果たします。

図3: Linear Technologyの RH108A オペアンプのPSRRプロットのビュー。(画像提供: Analog Devices Inc.)

ここでも、CMRRとCMRの場合と同様に、無次元のPSRRとデシベルで表される電源除去 (PSR) という用語は、半導体業界の文献では互換的に使用されます。

CMRRとの類似点がもう1つあります。理想的なシナリオでは、オペアンプの出力はDC周波数に相当しますが、より高い周波数でスパイクが発生します。つまり、周波数応答測定の尺度であるPSRRは、電源ラインに結合されたノイズを識別するための重要な要件です。

PSRR関連設計上の考慮事項

まず、低電圧電流源を使用して電源からの寄生ゲインを下げ、出力スイングに悪影響が及ばないようにします。次に、広範囲の電源で動作するオペアンプを使用します。これにより、設計者は電源電圧を変更してPSRRを測定し、電圧オフセットがどのように変化するかを確認できます。

さらに、オペアンプのデータシートには、電源ピンに流入する電流と出力端子に流出する電流に関する詳細が記載されています。これにより、設計者は特定の条件での総電力消費を計算できます。オペアンプのデータシートには、熱抵抗と最大接合部温度定格に関する詳細も記載されており、開発者はこれを使用してオペアンプ デバイスの消費電力制限を計算できます。

CMRRとPSRRが重要な理由

オペアンプは、アナログ信号を処理するシステムとのインターフェースから電圧増幅デバイスに至るまで、幅広い設計で広く使用されているチップです。したがって、設計エンジニアはCMRR値やPSRR値などの主要な特性を完全に理解することが不可欠です。

電子設計はより高い帯域幅へと移行しており、ノイズやEMIに関連する設計上の問題がさらに重要になるため、CMRRとPSRRを明確に理解することが特に重要です。同様に、より効率的な電力システムを求めるには、よりスマートな電源設計が必要です。

さらに、CMRRやPSRRなどのオペアンプのパラメータに関しては、これらの概念を説明するために冗長な用語が使用されているため、業界メディアの内容には多くの曖昧さがあります。この記事では、業界の頭字語の多さについて疑問を解消します。