지금은 전보다 많은 엔지니어들이 실리콘(Si) 기반 컴포넌트보다 높은 효율성, 전력 밀도, 전반적으로 더 나은 시스템 비용 효과를 얻기 위해 실리콘 카바이드(SiC) 기반 제품을 선택하고 있습니다.

엔지니어가 자신의 설계 목표를 달성하기 위해서는 SiC와 Si에 공통적으로 적용되는 기본적인 설계 원칙을 넘어서 SiC 만의 특성, 기능 및 장점을 고려해서 모델링 및 시뮬레이션을 수행해야 합니다.

Si에서와 같이 SiC도 여러 공급업체에서 제공되는 최적화된 도구 및 모델이 있으며, 표준 모델링 완화 방식을 적용할 수 있습니다. LTSpice, PLECS 및 Wolfspeed의 SpeedFit 2.0 Design Simulator™ 같은 도구들 간에 차이가 있지만, Wolfspeed의 전력 전문가들의 조언에 따라 SiC에서 시뮬레이션 정확도를 얻을 수 있습니다.

LTSpice를 사용한 정적 시뮬레이션

Wolfspeed의 Spice 모델은 25ºC 및 150ºC에 맞게 최적화되어 있습니다. 바디 다이오드 작업은 3세대 장치의 경우 -4V, 2세대 장치의 경우 -5V의 구동 전압 VGS로 최적화되어 있습니다. 엔지니어는 자체 발열 및 임시 열 기능과 기생 인덕턴스를 사용할 수 있습니다. 하지만 기생 양극성 및 관련 효과, 애벌랜치 배율 프로세스, 게이트-소스를 사용한 바디 다이오드 턴온 전압 변동은 모델링되지 않습니다.

LTSpice 정적 시뮬레이션 결과(여러 VGS 값의 IV 곡선 및 바디 다이오드 곡선)는 실제 측정과 효과적으로 일치합니다. 입력 정전용량 Ciss와 출력 정전용량 Coss 그리고 역절환 정전용량 Crss를 포함한 정전용량의 경우에도, 정적 시뮬레이션 결과가 해당 목적에 상당히 근접합니다. 따라서 엔지니어는 Spice 모델리의 정적 매개변수에 확신을 가질 수 있습니다.

더블 펄스 테스트

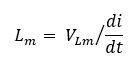

동적 동작을 이해하기 위한 일반적인 특성 벤치마크는 하프 브리지 더블 펄스 테스트입니다. 기생과 같은 어떤 고려도 없이 모델링할 때는 시뮬레이션이 측정된 결과와 상당히 멀어집니다(그림 1). 에너지 소비가 효율성에 영향을 주기 때문에 이렇게 큰 차이는 열 계산에 중요한 영향을 줍니다.

그림 1: 이상적인 더블 펄스 테스트 시뮬레이션 전환 손실 결과는

DUT, U2에 대한 데이터시트의 결과보다 약 45% 더 낮습니다.

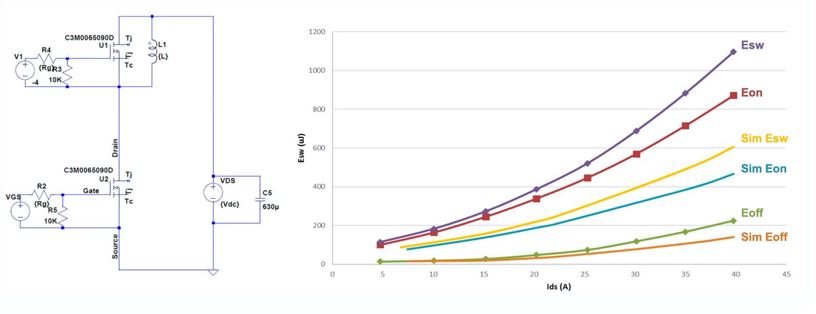

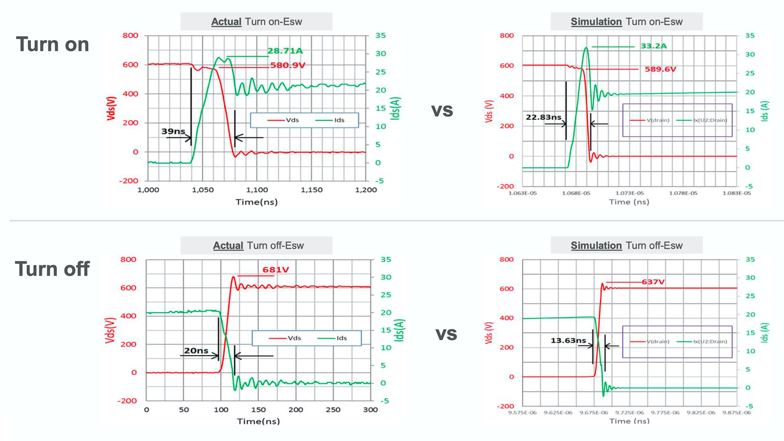

테스트 케이스에서는 장 펄스 다음에 1µs 갭이 오고, 그 다음 단 펄스가 옵니다. 턴온 및 턴오프는 Si 기반 장치에서와 같이 기존 방식으로 측정됩니다. 파형을 자세히 살펴보면(그림 2) 실제 결과와 이상적인 시뮬레이션된 결과 사이의 차이를 확인할 수 있습니다. 실제 결과는 인덕턴스(두 장치 사이의 기생 누설 인덕턴스 Lm, 패키지의 소스 인덕턴스인 패키지 인덕턴스 Lpkg)의 영향을 받기 때문에 시뮬레이션의 상승 및 하강 시간이 모두 측정된 것보다 빠릅니다. 또한 턴온 및 턴오프에 대한 오버슈트 결과 사이에도 차이가 있습니다. 이러한 차이는 전환 손실에서 전반적인 차이에 영향을 줍니다.

그림 2: 파형 비교를 통해 실제 턴온 상승 시간이 시뮬레이션된 상승 시간 22.83ns보다

훨씬 빠른 39ns이고 실제 하강 시간은 시뮬레이션된 하강 시간 13.63ns보다

느린 20ns인 것을 알 수 있습니다.

정확한 모델을 얻기 위해서는 인덕턴스를 추출하고 LTSpice로 직접 가져와야 합니다. 반면에 PLECS의 열 모델에는 기생 컴포넌트가 포함되지 않습니다.

Lm 찾기

|

Lm은 하이 사이드 U1 장치의 소스와 로우 사이드 U2 장치의

설명: 이 수식은 23.1674 nH Lm 값을 제공합니다.

|

그림 3: 실제 파형에서 추출한 정보를 사용하여 Lm을 계산할 수 있습니다. |

동기 벅, 동기 부스트, 하프 브리지 또는 풀 브리지에 관계없이 설계에는 PCB를 통해 하이 사이드 및 로우 사이드 장치 구성이 사용될 수 있습니다. 효과적인 레이아웃 방식을 따를 경우 Lm은 20nH ~ 25nH 범위에 포함됩니다. 엔지니어는 이를 시뮬레이션 시 사용할 기본 원칙으로 고려할 수 있습니다.

Lpkg 추출

설계자는 Lpkg가 TO-247과 같은 표준 패키지 공급업체 간에 동일할 것으로 예상할 수 있습니다. 하지만 선행 프레임 두께, 소스 와이어 결합, 패키지 숄더 길이의 차이로 인해 편차가 있습니다. 데이터시트에 제공된 경우 모델에 쉽게 연결할 수 있습니다. 그렇지 않으면 측정된 파형에서 추출하고 현재 패키지의 예상 값으로 추론할 수 있습니다.

설명:

VLpkg = Vds — VLds + Vdson = —11.515 V

Lds = 6.5372 nH, Spice 모델,

Vds = ~-27.8 V, 실제 파형,

VLds = -15.035 V,

Vds_on @ 20 A = 1.25 V, C3M0065090D 데이터시트 및

di/dt = -2.3 x 109

그림 4: 계산된 인덕턴스를 LTSpice 모델에 추가하면

실제 측정과 비슷하게 됩니다.

이 예시에서는 Lpkg 값으로 2.503 nH를 지정합니다. 편차가 있더라도 이 값은 올바른 예상값 및 신뢰할 수 있는 규칙으로 사용될 수 있습니다. 인덕턴스를 고려한 후 시뮬레이션하면 동적 모델 정확도가 향상됩니다(그림 4).

인덕턴스를 고려한 상태로 실제 및 시뮬레이션된 더블 펄스 테스트에 대한 Eon 및 Eoff 외에도 총 전환 에너지 Esw가 매우 근접합니다(그림 5).

그림 5: 설정된 기생을 사용한 후의 시뮬레이션된 전환 손실은

C3M0065090D 데이터시트와 일치합니다.

Lm 및 Lpkg에 대해 이러한 기본 규칙을 따를 경우 엔지니어가 열 예산에 대해 상당히 정확한 손실 및 열 계산을 얻을 수 있습니다.

병렬화된 MOSFET

SiC MOSFET는 전력 수준은 물론 전류 전달 용량을 늘리기 위해 병렬로 배치되는 경우가 많습니다. 하지만 이 때는 몇 가지 항을 고려해야 합니다.

- • 임계 전압 VTH 차이로 인한 전류 불균형

- • 비대칭 기생 인덕턴스로 인한 전류 불균형

- • 게이트 드라이브 진동

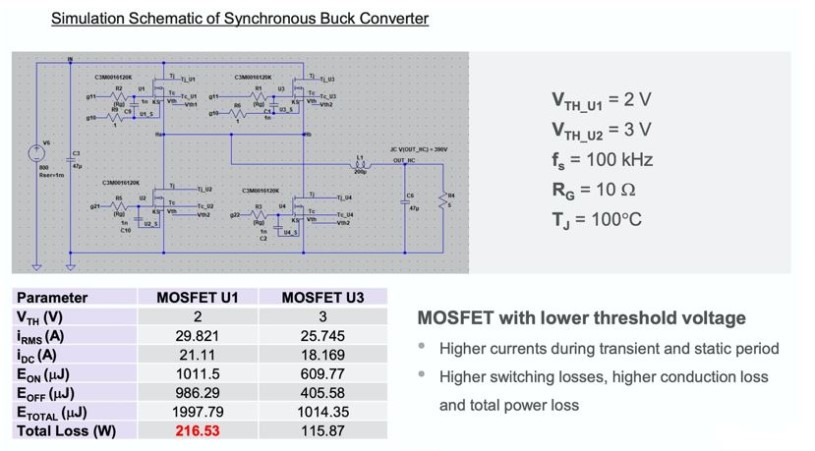

Wolfspeed SiC MOSFET를 사용할 경우 장치 특성이 불일치할 가능성이 거의 업습니다. 하지만 엔지니어가 공차 사양이 더 넓은 다른 SiC 파트를 사용해야 할 수 있고, 2 V VTH 장치와 3 V 장치를 선택할 수 있습니다. 임계값이 낮은 장치는 과도가 더 높고 이로 인해 전환 손실 및 전도 손실이 더 높으며, 따라서 총 전력 손실도 높습니다(그림 6).

그림 6: 전류 불균형으로 인해 2 V 장치의 총 손실이 3 V 장치의

총 손실의 거의 2배입니다.

두 장치 모두 게이트 저항 RG가 동일하고 동일한 온도 및 전환 주파수에서 작동하지만, 이러한 고려 없이 모델링하면 결과적으로 U1의 총 손실이 200 W를 초과하고 U3는 100 W만 조금 넘을 수 있습니다. 시뮬레이션된 파형은 정상 상태 50 A로 하강하기 전 UI의 최대 사용량이 약 70 A로 오버슈트되었고, 반면에 U3는 최대 사용량이 약 49 A이고 30 A 정상 상태로 안정화되는 것을 보여줍니다. 따라서 턴온 및 턴오프 시간 사이의 약간의 차이 외에도 두 장치 간의 전류 전달 용량에 큰 불일치가 있습니다.

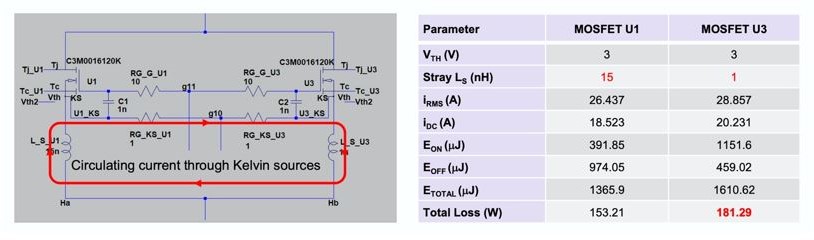

전류 불균형의 두 번째 원인은 비대칭 기생입니다. VTH는 동일하지만 소스 인덕턴스가 다른 두 장치 U1 및 U3(그림 7)가 있다고 가정해보십시오. 이것은 누설 인덕턴스, 게이트 드라이브 및 드레인 전류 간에 di/dt, 전압 불균형을 일으킵니다. 시뮬레이션된 파형은 U3에 대해 전류가 훨씬 빠르게 상승 및 하강하고, IDC 및 IRMS에 대해 더 높은 값에 도달하여 MOSFET에서 전환 손실이 17.9% 더 높고, 총 손실이 18.3% 더 높은 것을 보여줍니다.

그림 7: 이 예시에서는 U1 및 U3의 누설 인덕턴스 Ls 차이를

과장해서 보여줍니다. 이러한 과장은 불일치로 인한 영향을

보여주기 위한 것입니다.

적정 설계에서의 불일치 완화

불일치 MOSFET의 영향은 적절한 설계 방식을 따름으로써 크게 줄일 수 있습니다. 한 가지 예시로, 60 kW 태양광 인버터 부스트 참조 설계 CRD60DD12N에 2개의 75 mΩ 1,200 V C3M075120K MOSFET가 병렬로 사용된다고 가정해보십시오(그림 8). 올바른 설계 방식을 따른다면 60파트 샘플에서 최고 및 최저 VTH로 TO-247 4-리드 MOSFET 2개를 사용해도 올바르게 작동하는 하드웨어를 얻을 수 있습니다.

그림 8: VTH 차이가 있어도 이 테스트 회로에서는

장치 불일치 효과가 최소화되어 있습니다.

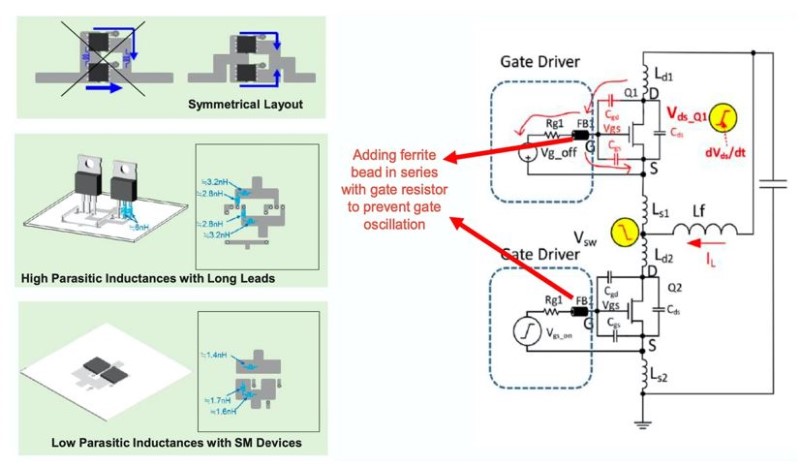

병렬화된 스위치의 게이트 루프에서 순환 전류를 줄이기 위해서는 대칭적 PCB 레이아웃이 중요합니다. 게이트 루프에서 전력 루프를 분리하고, 게이트 진동 방지를 위해 충분한 제동을 제공하고, 게이트에서 파트 손상을 일으킬 수 있는 전압 스파이크 및 링잉을 줄이기 위해 게이트 레그에 페라이트 비즈를 추가할 수 있습니다(그림 9).

그림 9: 밀접한 대칭 레이아웃, 균형적인 신호, 전력과 게이트 루프 분리,

게이트 진동을 방지하기 위한 제동, 링잉 감소를 위한 페라이트 비즈를 사용한

소형 RG 등 올바른 설계 방식을 모두 조합하여 전류 불균형을

줄일 수 있습니다.

이러한 설계 방식으로 인해 테스트 회로의 Q1은 총 전류의 47.6%를 전달하고, Q2는 52.4%를 전달하여, 장치 불일치에도 불구하고 수용 가능한 실질적인 결과에 도달합니다.

도구 선택 증가

SiC 기반 설계는 Wolfspeed의 SpeedFit, LTSpice 또는 PLECS를 사용하여 모델링될 수 있습니다. SpeedFit 및 LTSpice는 Wolfspeed에 등록하여 자유롭게 사용할 수 있지만, PLECS는 유료 구독이 필요합니다. 두들 간의 차이는 기생 처리, 손실 계산 등 시뮬레이션을 생성하는 방식 및 한계에 모두 영향을 줍니다.