现在,工程师们比以往任何时候都更倾向于选择基于碳化硅 (SiC) 的产品,因为它们比基于硅 (Si) 的元件具有更高的效率、功率密度和更好的整体系统成本效益。

除了 SiC 和 Si 之间共有的基本设计原则,以及牢记 SiC 不同的特性、能力和优势之外,工程师还必须进行建模和仿真,以确保能够达到他们的设计目标。

与 Si 一样,SiC 现在有来自不同供应商的优化工具和模型,并可应用标准的建模缓解措施。虽然 LTSpice、PLECS 和 Wolfspeed 的 SpeedFit 2.0 Design Simulator™ 等工具之间存在差异,但 Wolfspeed 的电源专家可提供有助于实现 SiC 的仿真精度的秘诀。

使用 LTSpice 进行静态仿真

Wolfspeed 的 Spice 型号针对 25°C 和 150°C 进行了优化。本体二极管的操作针对驱动电压进行了优化,第 3 代器件的驱动电压 VGS 为 -4 V,第 2 代器件为 -5 V。工程师可添加自热和瞬态热能力以及寄生电感。然而,寄生双极效应和相关效应、雪崩倍增过程以及本体二极管导通电压随栅极到源极的变化并未建模。

LTSpice 静态仿真结果,即各种 VGS 值下的 IV 曲线和本体二极管曲线,与实际测量结果吻合度很高。对于电容,包括输入电容 Ciss、输出电容 Coss 以及反向转移电容 Crss,静态仿真结果与用途相当接近。因此,工程师可以对 Spice 建模的静态参数充满信心。

双脉冲测试

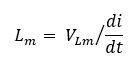

了解动态行为的典型表征基准是半桥双脉冲测试。在不考虑任何因素(如寄生)的情况下进行建模时,仿真结果与测量结果相差甚远(图 1)。由于能耗影响效率,如此巨大的差异对热计算有显著的影响。

图 1:理想的双脉冲测试仿真开关损耗结果

比被测器件 U2 的数据表中的值低 45% 左右。

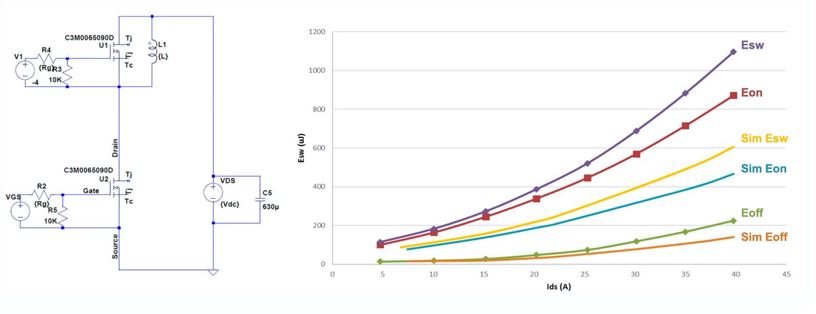

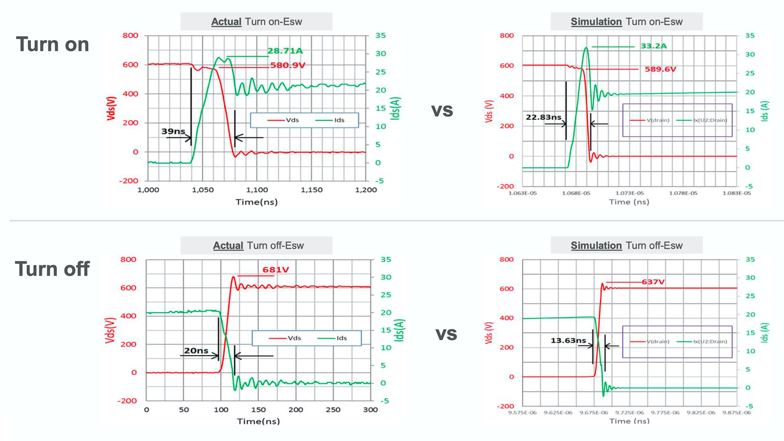

在测试案例中,一个长脉冲之后是 1 μs 的间隙,之后是短脉冲。与基于 Si 的器件一样,导通和关断采用传统测量方法。仔细观察波形(图 2),就会发现实际仿真结果和理想仿真结果之间的差异。仿真中的上升和下降时间都比测量结果快很多,因为实际结果受到电感的影响,即两个器件之间的寄生杂散电感 Lm,以及封装电感 Lpkg,即封装的源极电感。导通和关断的过冲结果也存在差异。这些差异导致开关损耗的总体差异。

图 2:对比波形可以发现,

实际导通上升时间为 39 ns,仿真时间快很多,为 22.83 ns;

实际下降时间为 20 ns,而仿真时间为 13.63 ns。

为获得一个精确的模型,必须提取电感并手动导入 LTSpice 中。另一方面,PLECS 中的热模型不包含寄生元件。

查找 Lm

|

Lm 是

其中: 这样即可得出 Lm 的值为 23.1674 nH。

|

图 3:从实际波形中提取的信息 可用于计算 Lm。 |

无论是同步降压、同步升压、半桥还是全桥,设计很可能通过 PCB 采用高侧和低侧器件的配置。如果遵循良好的布局实践,Lm 在 20 nH 至 25 nH 范围内。工程师们可以将此视为仿真中使用的经验法则。

提取 Lpkg

设计人员可能期望,对于 TO-247 等标准封装,各供应商的 Lpkg 都是相同的。然而,由于引线框架的厚度、源极引线接合法以及封装肩部长度的不同,差异在所难免。数据表中如有提供,则可以轻松插入到模型中。如未提供,则可以从测量的波形中提取出来,并推断手头封装可能的良好估计值。

其中:

VLpkg = Vds — VLds + Vdson = —11.515 V

Lds = 6.5372 nH(来自 Spice 模型),

Vds = ~-27.8 V(来自实际波形),

VLds = -15.035 V,

Vds_on @ 20 A = 1.25 V(来自 C3M0065090D 数据表),

di/dt = -2.3 x 109

图 4:将计算出的电感值添加到 LTSpice 模型中,

使其接近实际测量值。

在我们的例子中,得出的 Lpkg 值为 2.503 nH。尽管存在变化,但这个值可以作为良好的估计值和可靠的经验法则。考虑电感后进行仿真,可以使动态模型更加精确(图 4)。

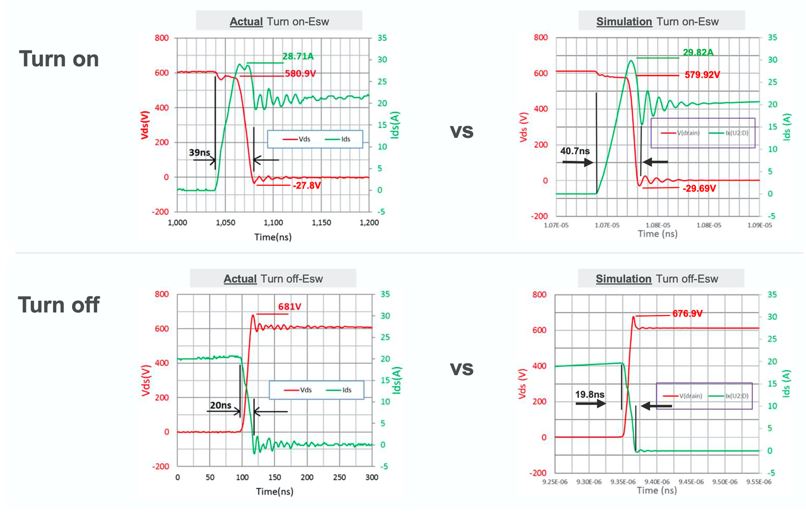

考虑电感因素后,实际和仿真双脉冲测试的总开关能量 Esw 以及 Eon 和 Eoff 变得非常接近(图 5)。

图 5:使用设置寄生后,仿真的

开关损耗与 C3M0065090D 数据表相一致。

利用 Lm 和 Lpkg 的这些经验法则,工程师可以为热预算获得相当准确的损耗和热计算。

并联 MOSFET

SiC MOSFET 通常并联放置,以提高载流能力和功率水平。然而,一些注意事项需要牢记:

- •阈值电压 VTH 差值导致的电流不平衡

- • 非对称寄生电感导致的电流不平衡

- • 栅极驱动振荡

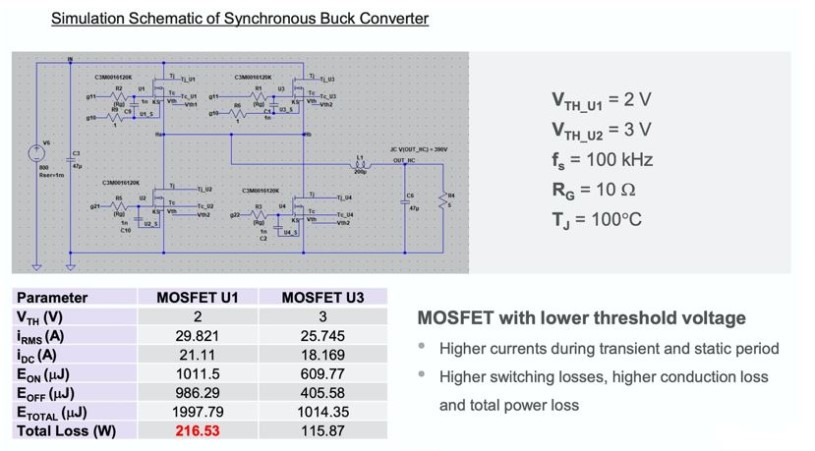

使用 Wolfspeed SiC MOSFET,器件特性失配的可能性很小。然而,工程师可能需要使用规格容差更大的其他 SiC 零部件,例如可能选择 VTH 为 2 V 的某个器件,并选择阈值电压为 3 V 的另一个器件。阈值较低的器件具有更高的瞬态,因此,开关损耗和传导损耗更高,导致总功率损耗更高(图 6)。

图 6:由于电流不平衡,2 V 器件的总损耗

几乎是 3 V 器件的两倍。

虽然两个器件具有相同的栅极电阻 RG,并在相同的温度和开关频率下工作,但在不考虑任何因素的情况下进行建模,结果是 U1 的总损耗超过 200 W,而 U3 仅超过 100 W。仿真波形显示,U1 在下降到 50 A 的稳态之前,峰值达到约 70 A 的过冲,而 U3 达到大约 49 A 的峰值后,稳定在 30 A 的稳态。因此,这两个器件的载流能力相当失配,导通和关断时间也有轻微差异。

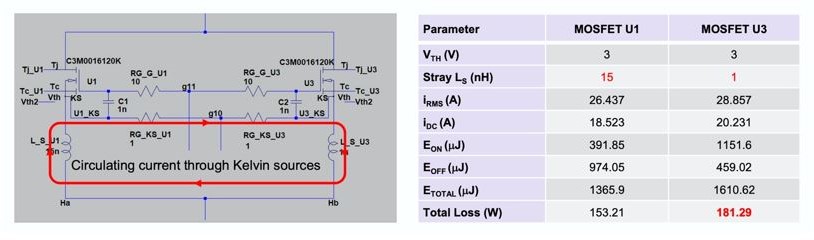

电流不平衡的第二个原因是非对称寄生。例如 U1 和 U3 这两个器件(图 7)具有相同的 VTH,但源极电感不同。这导致 di/dt、杂散电感电压、栅极驱动和漏极电流相当不平衡。仿真波形显示,U3 的电流上升和下降速度快得多,IDC 和 IRMS 也达到更高的值,导致该 MOSFET 的开关损耗和总损耗分别高 17.9% 和 18.3%。

图 7:此示例夸大了 U1 和 U3 的杂散电感 Ls 的差异,

以证明

失配的影响。

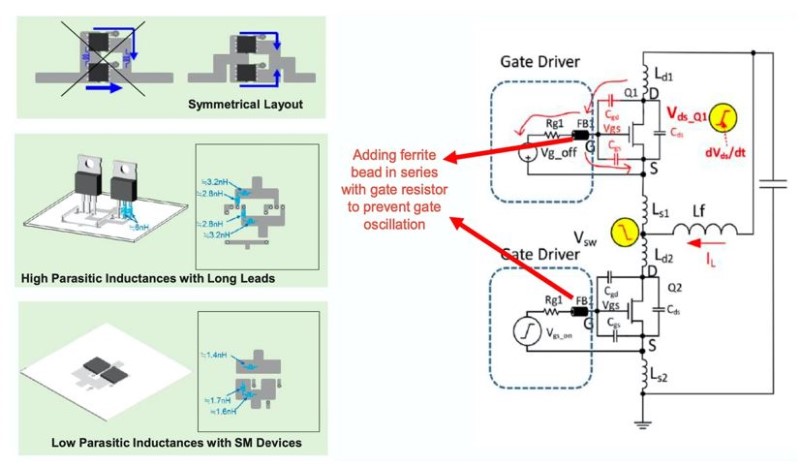

通过良好的设计缓解失配问题

通过结合良好的设计实践,可以显著降低 MOSFET 失配的影响。以 60 kW 太阳能逆变器升压参考设计 CRD60DD12N 为例,该设计并联使用两个 75 mΩ 1,200V C3M075120K MOSFET(图 8)。如果采用良好的设计实践,从 60 个零部件的样品中使用具有最高和最低 VTH 的两个 TO-247 4-引脚 MOSFET,仍然可以实现良好的硬件运行。

图 8:尽管存在 VTH 差异,

在该测试电路中,器件失配的影响被最小化。

对称的 PCB 布局对于减少并联开关的栅极环路中的循环电流至关重要。将电源环路与栅极环路分开,提供足够的阻尼以防止栅极振荡,并在栅极引脚处增加一个铁氧体磁珠,以减少栅极上可能导致部件损坏的电压尖峰和振铃(图 9)。

图 9:良好的设计实践 – 紧密对称的布局、平衡的

信号、电源和栅极环路的分离、防止

栅极振荡的阻尼、具有铁氧体磁珠以减少振铃的小 RG,

所有这些结合在一起以减少电流不平衡。

由于这些设计实践,测试电路中 Q1 承载的电流占总电流的 47.6%,而 Q2 承载的电流占 52.4%,因此尽管器件失配,但还是能够达到可接受的实际结果。

增加工具选择

基于 SiC 的设计可使用 Wolfspeed 的 SpeedFit、LTSpice 或 PLECS 进行建模。SpeedFit 和 LTSpice 可以通过注册 Wolfspeed 免费使用,而 PLECS 则需要支付订阅费。这些工具之间的差异会影响到产生仿真的方式,也会影响它们的局限性,例如在处理寄生和计算损耗方面。