Ahora más que nunca, los ingenieros eligen productos a base de carburo de silicio (SiC) debido a su mayor eficiencia, su densidad de potencia y su mayor rentabilidad general del sistema en comparación con componentes a base de silicio (Si).

Más allá de los principios de diseño básicos comunes entre el SiC y el Si, y la necesidad de tener en cuenta las diferentes características, capacidades y ventajas del SiC, los ingenieros deben realizar modelado y simulación para poder cumplir con sus objetivos de diseño.

Al igual que con el Si, el SiC ahora cuenta con herramientas y modelos optimizados disponibles de diversos proveedores, y pueden aplicarse mitigaciones de modelado estándar. Si bien existen diferencias entre herramientas tales como LTSpice, PLECS y el simulador de diseño SpeedFit 2.0 de Wolfspeed™, los consejos de los expertos en energía de Wolfspeed ayudarán a alcanzar la precisión de simulación con SiC.

Simulación estática con LTSpice

Los modelos Spice de Wolfspeed están optimizados para 25 ºC y 150 ºC. La operación del diodo de cuerpo está optimizada para una tensión de transmisión, VGS, de -4 V para dispositivos Gen 3 y de -5 V para Gen 2. Los ingenieros pueden incorporar autocalentamiento y capacidad térmica transitoria e inductancia parásita. Sin embargo, el efecto bipolar parásito y otros efectos asociados, el proceso de multiplicación en avalancha y la variación de la tensión de encendido del diodo de cuerpo con compuerta a fuente no se modelan.

Los resultados de la simulación estática LTSpice (la curva IV a diversos valores VGS y la curva del diodo de cuerpo) se corresponden bien con los resultados reales. Para capacitancias (capacitancia de entrada, Ciss, capacitancia de salida, Coss, y capacitancia de transferencia inversa, Crss), los resultados de la simulación estática son también bastante cercanos para el objetivo. Por lo tanto, los ingenieros puede sentirse seguros de los parámetros estáticos del modelado Spice.

Una prueba de doble pulso

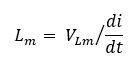

Un punto de referencia de caracterización típico para comprender el comportamiento dinámico es una prueba de doble pulso y medio puente. Cuando se modela sin tomar ningún factor, como los parásitos, en consideración, la simulación se aleja significativamente de los resultados medidos (Figura 1). Dado que el consumo de energía tiene un impacto en la eficiencia, una diferencia así de grande tiene un efecto significativo en los cálculos térmicos.

Figura 1: Los resultados ideales de pérdida de conmutación de una prueba de doble pulso son

alrededor de un 45 % más bajos en la hoja de datos para el DUT, U2.

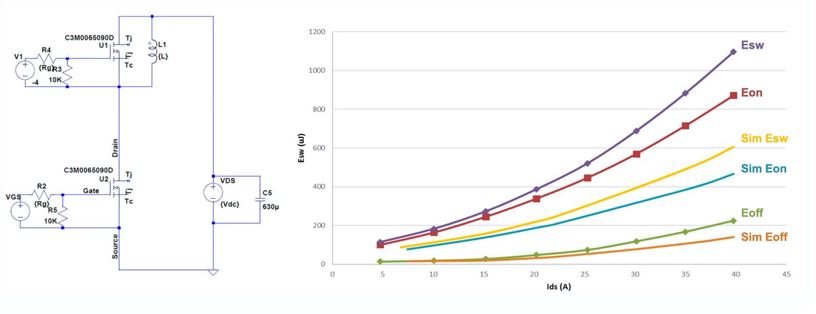

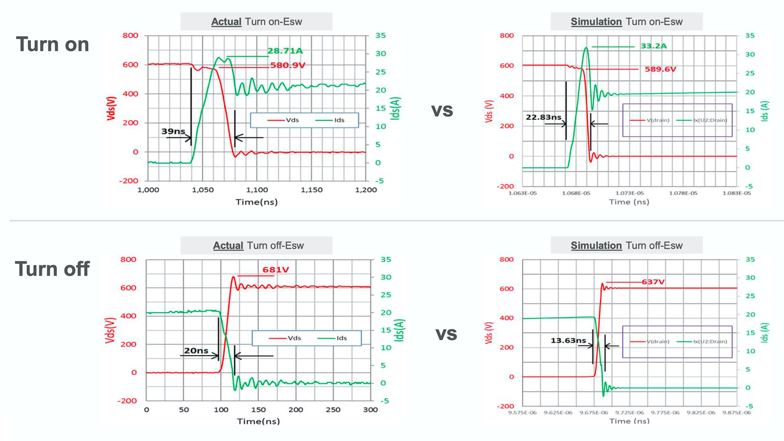

En el caso de la prueba, a un pulso largo lo sigue un intervalo de 1 µs, al cual lo sigue un pulso breve. El encendido y apagado se miden de la misma forma convencional utilizada en dispositivos a base de Si. Al mirar más de cerca las formas de onda (Figura 2), se destaca la diferencia entre los resultados simulados reales e ideales. Los tiempos de ascenso y de caída en la simulación son muchos más rápidos que los medidos, ya que los resultados reales se ven afectados por inductancias: inductancia parásita, Lm, entre los dos dispositivos, e inductancia de paquete, Lpkg, que es la inductancia de origen del paquete. También existe una diferencia entre los resultados de sobreimpulso para el encendido y el apagado. Estas diferencias contribuyen a la diferencia general en las pérdidas de conmutación.

Figura 2: Una comparación de las formas de onda revela que el tiempo real

de subida de encendido es 39 ns, frente al tiempo mucho menor de 22,83 ns simulado

y el tiempo de caída real es de 20 ns frente a los 13,36 ns simulados.

Para obtener un modelo adecuado, las inductancias deben extraerse e importarse manualmente a LTSpice. El modelado térmico en PLECS, por otro lado, no incluye componentes parásitos.

Encontrar Lm

|

Lm es la inductancia entre la fuente del dispositivo

Donde: Esto entrega un valor de 23,1674 nH para Lm.

|

Figura 3: La información extraída de la forma de onda real puede usarse para calcular Lm. |

Ya sea un buck sincrónico, boost sincrónico, medio puente o puente completo, es probable que el diseño use una configuración de dispositivos de lado alto y de lado bajo mediante un PCB. Si se siguen buenas prácticas de diseño, Lm se encuentra en el rango de 20 nH a 25 nH. Los ingenieros pueden considerar ello como la regla de oro a usar en simulaciones.

Extracción de Lpkg

Los diseñadores pueden esperar que Lpkg sea el mismo en distintos proveedores en paquetes estándar, tales como el TO-247. Sin embargo, existen variaciones a causa de las diferencias en el espesor de los marcos de conductores, en la conexión de los cables de fuente y en la longitud del hombro en el paquete. Si está disponible en una hoja de datos, puede conectarse fácilmente al modelo. Si no, puede extraerse de una forma de onda medida y extrapolarse a lo que podría ser una buena estimación para el paquete en cuestión.

Donde:

VLpkg = Vds — VLds + Vdson = —11,515 V

Lds = 6,5372 nH a partir del modelo Spice,

Vds = ~-27,8 V a partir de la forma de onda real,

VLds = -15,035 V,

Vds_on a 20 A = 1,25 V a partir de la hoja de datos C3M0065090D, y

di/dt = -2,3 x 109

Figura 4: Añadir las inductancias calculadas al modelo

LTSpice lo acerca a las medidas reales.

En nuestro ejemplo, esto entrega un valor Lpkg de 2,503 nH. A pesar de las variaciones, este valor puede tomarse como una buena estimación y una regla de oro confiable. Realizar la simulación luego de tomar en consideración las inductancias permite que el modelo dinámico sea preciso (Figura 4).

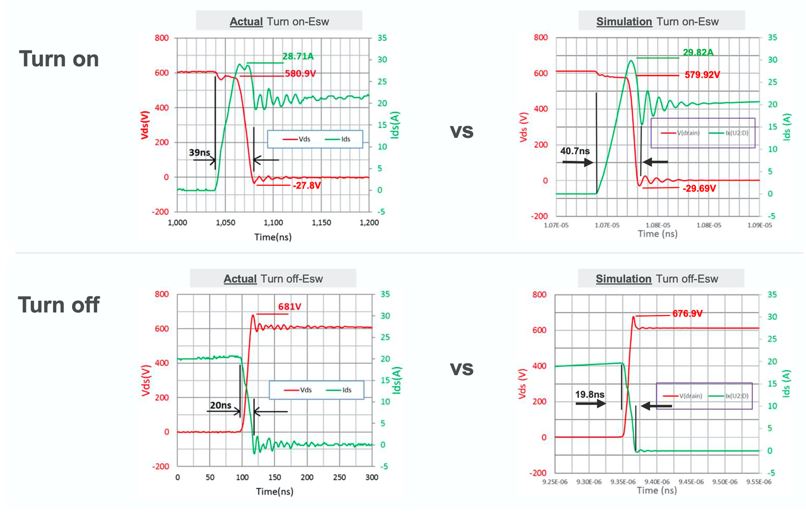

Con las inductancias ponderadas, el Esw de energía de conmutación total, al igual que Eon y Eoff, para la prueba de doble pulso real y simulada se acercan mucho (Figura 5).

Figura 5: Luego de usar los parásitos de configuración, las pérdidas

de conmutación simuladas coinciden con la hoja de datos C3M0065090D.

Usando la regla de oro para Lm y Lpkg, los ingenieros pueden obtener cálculos térmicos y de pérdida bastante precisos para su presupuesto térmico.

MOSFET en paralelo

Los MOSFET de SiC con frecuencia se colocan en paralelo para aumentar la capacidad de carga de corriente y los niveles de potencia. Sin embargo, estas son algunas consideraciones que se deben tener en cuenta:

- • Desequilibrio de corriente a causa de diferencias en la tensión de umbral, VTH.

- • Desequilibrio de corriente a causa de inductancias parásitas asimétricas.

- • Oscilación del controlador de compuerta.

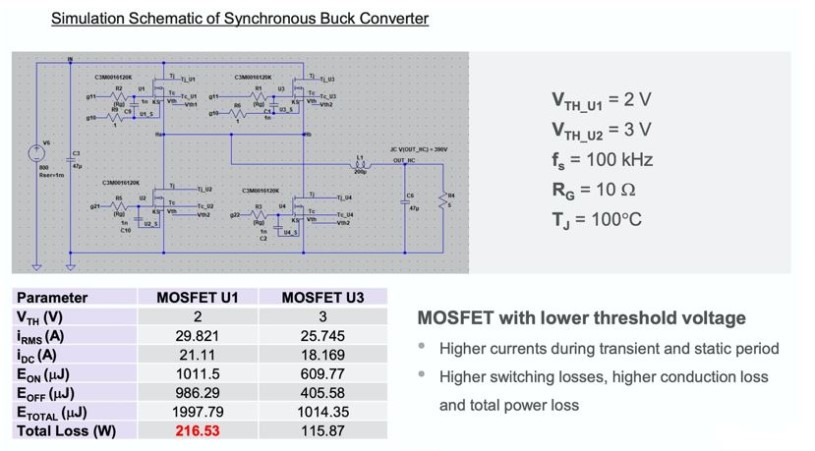

Con los MOSFET de SiC de Wolfspeed, existe una pequeña posibilidad de discrepancia con las características del dispositivo. Sin embargo, los ingenieros podrían tener que usar otras piezas de SiC con una tolerancia de especificación más alta, y podrían elegir, por ejemplo, un dispositivo con VTH de 2 V y otro de 3 V. El dispositivo con el umbral más bajo tiene una mayor transitoriedad y, por ello, mayores pérdidas de conmutación y de conducción. Por lo tanto, tiene mayores pérdidas de energía total (Figura 6).

Figura 6: Las pérdidas totales del dispositivo de 2 V son casi el doble que las

del dispositivo de 3 V a causa del desequilibrio de corriente.

Si bien ambos dispositivos tienen la misma resistencia de compuerta, RG, y están operando a la misma temperatura y frecuencia de conmutación, modelar sin ninguna consideración tiene como resultado que U1 tenga más de 200 W de pérdidas totales, y U3 solo un poco más de 100 W. Las formas de onda simuladas muestran que U1 alcanza su punto máximo a un sobreimpulso de alrededor de 70 A antes de caer al estado constante de 50 A, mientras que U3 alcanza su punto máximo a cerca de 49 A y se asienta en un estado constante de 30 A. Por lo tanto, existe una discordancia considerable en la capacidad de carga de corriente entre ambos dispositivos, al igual que pequeñas diferencias en los tiempos de encendido y apagado.

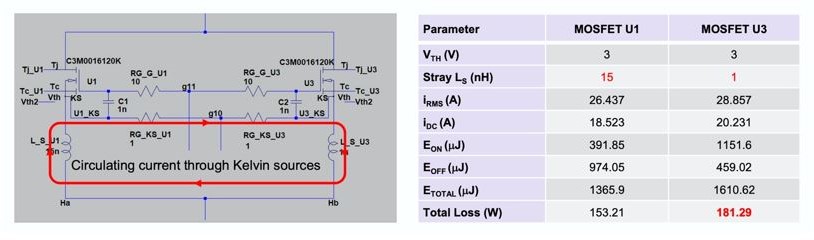

La segunda causa de desequilibrio son los parásitos asimétricos. Piense en dos dispositivos, U1 y U3 (Figura 7) que tienen el mismo VTH, pero distintas inductancias de origen. Esto causa un desequilibrio considerable en la di/dt, las tensiones en las inductancias parásito, los controladores de compuerta y las corrientes de drenaje. Las formas de onda simuladas muestran que la corriente aumenta y disminuye mucho más rápido en U3, y alcanza valores más altos de IDC y IRMS, lo que causa una pérdida de conmutación un 17,9 % mayor y una pérdida total un 18,3 % mayor que en MOSFET.

Figura 7: La diferencia en Ls de inductancia parásita en U1

y U3 se exagera en este ejemplo para demostrar

el impacto de la discordancia.

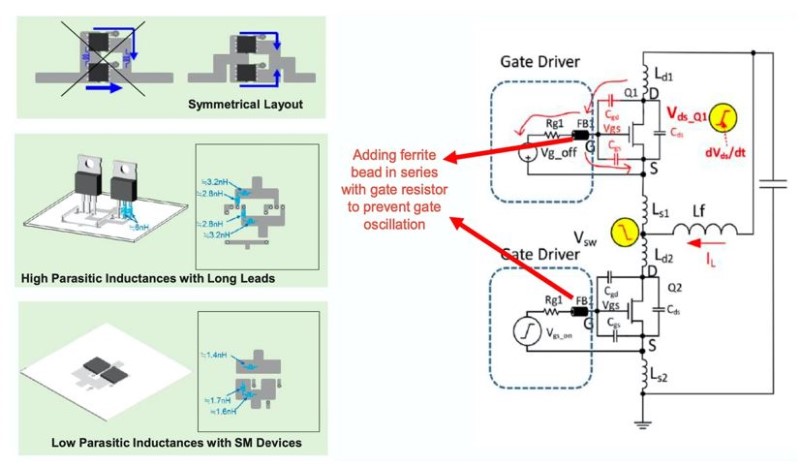

Mitigue la discordancia con un buen diseño

El impacto de los MOSFET discordes puede reducirse considerablemente cuando se incorporan buenas prácticas de diseño. Como ejemplo, piense en el diseño boost de referencia de un inversor solar de 60 kW, CRD60DD12N, que usa dos MOSFET C3M075120K de 75 mΩ y 1.200 V en paralelo (Figura 8). Usando dos de los MOSFET TO-247 de 4 conectores con los VTH más altos de una muestra de 60 piezas, aún se logra obtener un hardware que funciona bien, si se emplean buenas prácticas de diseño.

Figura 8: A pesar de la diferencia de VTH, los efectos

de la discordancia de dispositivos se minimizan en este circuito de prueba.

Un diseño de PCB simétrico es fundamental para reducir la corriente circulante en los bucles de compuerta de conmutadores en paralelo. Separe el bucle de potencia del bucle de compuerta, proporcione suficiente amortiguación para evitar la oscilación de compuertas y agregue un grano de ferrita a la pata de la compuerta para reducir los picos de tensión y el zumbido en la compuerta que podrían causar daño a las piezas (Figura 9).

Figura 9: Buenas prácticas de diseño: estricto diseño simétrico, señal

equilibrada, separación de los bucles de potencia y compuerta, amortiguación para evitar

la oscilación de compuerta y un RG pequeño con un grano de ferrita para reducir el zumbido;

todo se combina para reducir el desequilibrio de corriente.

A causa de estas prácticas de diseño, Q1 en el circuito de prueba carga el 47,6 % de la corriente total, mientras que Q2 carga el 52,4 %, por lo que alcanza resultados aceptables en el mundo real a pesar de la discordancia de dispositivos.

Aumentamos las opciones de herramientas

Los diseños a base de SiC pueden modelarse mediante SpeedFit, LTSpice o PLECS de Wolfspeed. Si bien SpeedFit y LTSpice pueden usarse de forma gratuita al registrarse con Wolfspeed, PLECS viene con una tarifa de suscripción. Las diferencias en las herramientas afectan la manera de generar simulaciones y también sus limitaciones, como en el manejo de parásito y el cálculo de pérdidas.