現在、エンジニアはこれまで以上に、シリコン (Si) ベースのコンポーネントよりも効率、電力密度、および全体的なシステムコスト効率が高いという理由で、シリコンカーバイド (SiC) ベースの製品を選択しています。

SiCとSiに共通する基本的な設計原則に加え、SiCのさまざまな特性、機能、利点を念頭に置く必要性に加えて、エンジニアは設計目標を確実に達成できるようにモデル化とシミュレーションを行う必要があります。

Siと同様に、SiCにもさまざまなサプライヤーから最適化されたツールとモデルが提供されており、標準的なモデリング緩和策を適用できます。LTSpice、PLECS、WolfspeedのSpeedFit 2.0設計シミュレーター™ などのツールには違いがありますが、Wolfspeedの電力専門家からのヒントは、SiCでのシミュレーション精度の実現に役立ちます。

LTSpiceによる静的シミュレーション

WolfspeedのSpiceモデルは25ºCおよび150ºCに最適化されています。ボディ ダイオードの動作は、第3世代デバイスでは -4 V、第2世代デバイスでは -5 Vの駆動電圧VGS に最適化されています。エンジニアは、自己発熱、過渡熱容量、および寄生インダクタンスを組み込むことができます。ただし、寄生バイポーラとそれに関連する効果、アバランシェ増幅プロセス、ゲートからソースへのボディダイオードのターンオン電圧の変化はモデル化されていません。

LTSpiceの静的シミュレーション結果 (さまざまなVGS値でのIV曲線とボディ ダイオード曲線) は、実際の測定値とよく一致しています。静電容量(入力静電容量Ciss、出力静電容量Coss、逆伝達静電容量Crss)についても、静的シミュレーションの結果は目的にかなり近いものとなっています。したがって、エンジニアはSpiceモデリングの静的パラメータに自信を持つことができます。

ダブルパルステスト

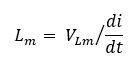

動的動作を理解するための一般的な特性評価ベンチマークは、ハーフブリッジ ダブルパルス テストです。寄生要素などを考慮せずにモデル化すると、シミュレーションは測定結果と大幅に異なります (図1)。エネルギー消費は効率に影響するため、このような大きな差は熱計算に大きな影響を与えます。

図1: 理想的なダブルパルス テスト シミュレーションのスイッチング損失の結果は、

DUT U2のデータシートに記載されている結果よりも約45% 低くなります。

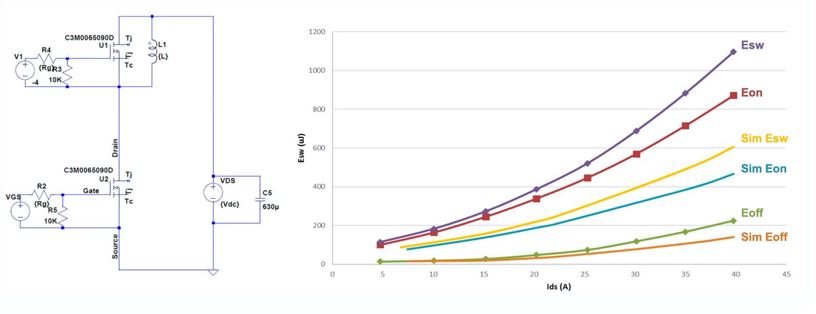

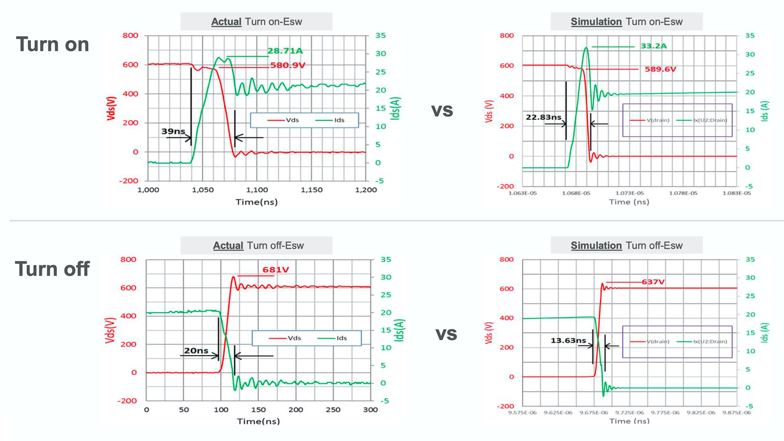

テストケースでは、長いパルスの後に1 µsのギャップが続き、その後に短いパルスが続きます。ターンオンとターンオフは、Siベースのデバイスの場合と同様に従来の方法で測定されます。波形 (図2) を詳しく見ると、実際のシミュレーション結果と理想的なシミュレーション結果の違いが強調されます。シミュレーションの立ち上がり時間と立ち下がり時間は、測定値よりもはるかに速くなります。これは、実際の結果がインダクタンス(2つのデバイス間の寄生浮遊インダクタンスLm と、パッケージのソース インダクタンスであるパッケージ インダクタンスLpkg)の影響を受けるためです。ターンオンとターンオフのオーバーシュート結果にも違いがあります。これらの違いは、スイッチング損失の全体的な違いに影響します。

図2: 波形を比較すると、実際のターンオン

立ち上がり時間は39 nsであるのに対し、シミュレーションでは22.83 nsとはるかに高速であり、実際の

立ち下がり時間は20 nsであるのに対し、シミュレーションでは13.63 nsであることがわかります。

正確なモデルを取得するには、インダクタンスを抽出し、手動でLTSpiceにインポートする必要があります。一方、PLECSの熱モデルには寄生成分は含まれません。

Lmを見つける

|

Lm は、ハイサイドU1デバイスのソースとローサイドU2デバイスのドレイン間のインダクタンスです。

ここで、 これにより、Lmの値は23.1674 nHになります。

|

図3: 実際の波形から抽出された情報 を使用して、Lm を計算できます。 |

同期降圧、同期昇圧、ハーフブリッジ、フルブリッジのいずれの場合でも、設計ではPCBを介してハイサイド デバイスとローサイド デバイスの構成が使用される可能性があります。適切なレイアウト方法に従うと、Lm は20 nH ~ 25 nHの範囲になります。エンジニアはこれをシミュレーションで使用する経験則として考えることができます。

Lpkgの抽出

設計者は、TO-247のような標準パッケージの場合、Lpkg がサプライヤー間で同じであると予想する場合があります。ただし、リードフレームの厚さ、ソースワイヤボンディング、パッケージのショルダーの長さの違いにより変動があります。データシートで利用可能な場合は、モデルに簡単に組み込むことができます。そうでない場合は、測定された波形から抽出し、手元のパッケージに適した推定値に外挿することができます。

どこ:

五LPkg = 五ds — V末日聖徒イエス・キリスト教会 + 五息子 = —11.515V

らds = 6.5372 nH(スパイスモデルより)

五ds = 実際の波形から約-27.8 V、

五末日聖徒イエス・キリスト教会 = -15.035 V、

五ds_on @ 20 A = 1.25 Vから C3M0065090D データシート、および

d/dt = -2.3 x 10 9

図4: 計算されたインダクタンスをLTSpiceに追加する

モデルは実際の測定値に近づきます。

この例では、Lパッケージ 値は2.503 nHです。変動はあるものの、この値は適切な推定値であり、信頼できる経験則として捉えることができます。インダクタンスを考慮してシミュレーションを行うと、動的モデルが正確になります(図4)。

インダクタンスを考慮すると、実際のダブルパルステストとシミュレーションによるダブルパルステストのスイッチングエネルギーEswとEonおよびEoffは非常に近くなります(図5)。

図5: セットアップ寄生効果を使用した後、シミュレーションされた

スイッチング損失はC3M0065090Dのデータシートと一致します。

Lm とLpkgにこれらの経験則を使用すると、エンジニアは熱予算の損失と熱の計算をかなり正確に行うことができます。

並列MOSFET

SiC MOSFETは、電流容量と電力レベルを高めるために並列に配置されることがよくあります。ただし、留意すべき点がいくつかあります。

- • 閾値電圧VTHの違いによる電流不均衡

- • 非対称寄生インダクタンスによる電流不均衡

- • ゲートドライブ振動

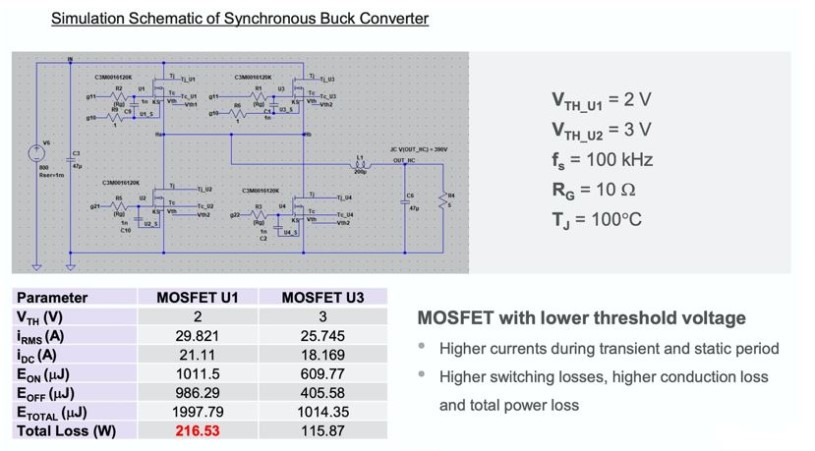

Wolfspeed SiC MOSFETでは、デバイス特性の不一致が発生する可能性はほとんどありません。ただし、エンジニアは、より広い仕様許容範囲を持つ他のSiC部品を使用する必要があり、たとえば、2 V VTH のデバイスと3 Vのデバイスを選択する場合があります。しきい値が低いデバイスは過渡電圧が高く、そのためスイッチング損失と伝導損失が高くなり、結果として総電力損失が高くなります (図6)。

図6: 電流の不均衡により、2 Vデバイスの合計損失は3 Vデバイスのほぼ2倍になります

。

両方のデバイスのゲート抵抗RG は同じで、同じ温度とスイッチング周波数で動作していますが、何も考慮せずにモデル化すると、U1の総損失は200 Wを超え、U3は100 Wをわずかに超えることになります。シミュレーション波形を見ると、U1は50 Aの定常状態に低下する前に約70 Aのオーバーシュートにピークを迎えますが、U3は49 Aのピークを迎えてから30 Aの定常状態に落ち着きます。したがって、2つのデバイス間の電流容量には大きな不一致があり、また、オン時間とオフ時間にもわずかな違いがあります。

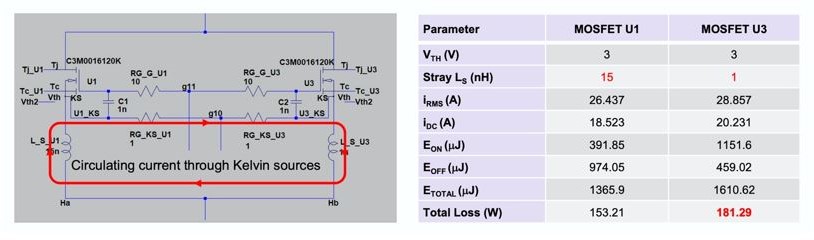

電流不均衡の2番目の原因は、非対称の寄生です。同じVTHを持ちながらソースインダクタンスが異なる2つのデバイスU1とU3 (図7 ) を考えます。これにより、di/dt、浮遊インダクタンスの電圧、ゲート ドライブ、およびドレイン電流にかなりの不均衡が生じます。シミュレーション波形を見ると、U3の電流の増減が非常に速く、IDC とIRMS の値が上昇し、その結果、MOSFETのスイッチング損失が17.9% 増加し、総損失が18.3% 増加していることがわかります。

図7: この例では、不一致の影響を示すために、U1とU3の浮遊インダクタンスL s

の差が誇張されています。

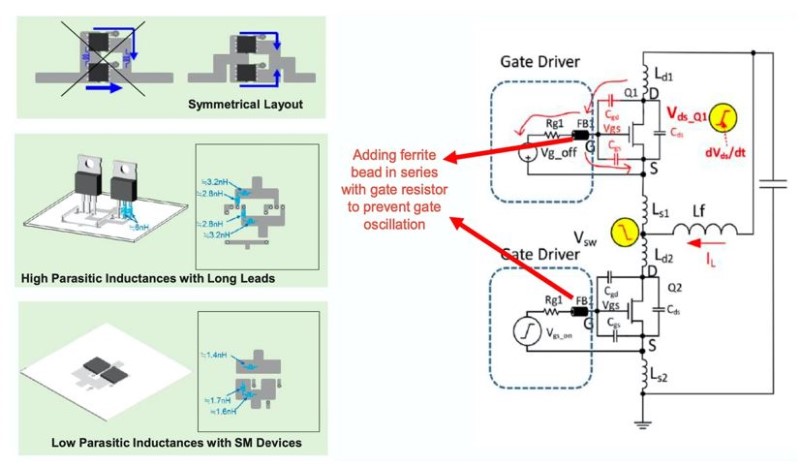

優れたデザインでミスマッチを軽減

適切な設計手法を取り入れることで、MOSFETの不一致の影響を大幅に軽減できます。例として、2つの75 mΩ 1,200V C3M075120K MOSFETを並列に使用する60 kWソーラー インバータ ブースト リファレンス デザインCRD60DD12Nを見てみましょう (図8)。60個の部品のサンプルから、最高と最低のVTH を持つTO-247 4リードMOSFETを2つ使用しても、適切な設計手法が採用されていれば、適切に動作するハードウェアを実現できます。

図8: VTH の違いにもかかわらず、このテスト回路ではデバイスの不一致の影響

が最小限に抑えられます。

対称的なPCBレイアウトは、並列スイッチのゲート ループ内の循環電流を減らすために重要です。電源ループをゲート ループから分離し、ゲートの振動を防止するために十分な減衰を提供し、ゲート レッグにフェライト ビーズを追加して、部品の損傷を引き起こす可能性のあるゲートの電圧スパイクとリンギングを低減します (図9)。

図9: 優れた設計プラクティス - 緊密な対称レイアウト、バランスのとれた信号、電源ループとゲート ループの分離、ゲート発振を防ぐためのダンピング

、およびリンギングを減らすためのフェライト ビーズを使用した小さなR

G - これらすべての組み合わせにより、電流の不均衡が軽減されます。

これらの設計手法により、テスト回路のQ1は総電流の47.6% を流し、Q2は52.4% を流すことになり、デバイスの不一致にもかかわらず、現実世界で許容できる結果が得られます。

ツールの選択肢を増やす

SiCベースの設計は、WolfspeedのSpeedFit、LTSpice、またはPLECSを使用してモデル化できます。SpeedFitとLTSpiceはWolfspeedに登録することで無料で使用できますが、PLECSにはサブスクリプション料金がかかります。ツール間の違いは、シミュレーションの生成方法と、寄生要素の処理や損失の計算などの制限の両方に影響します。