Aujourd'hui plus que jamais, les ingénieurs choisissent des produits à base de carbure de silicium (SiC) pour leur efficacité supérieure, leur densité de puissance et leur meilleure rentabilité globale du système par rapport aux composants à base de silicium (Si).

Au-delà des principes de conception de base communs au SiC et au Si, et de la nécessité de garder à l'esprit les différentes caractéristiques, capacités et avantages du SiC, les ingénieurs doivent modéliser et simuler pour s'assurer qu'ils atteindront leurs objectifs de conception.

Comme pour le Si, le SiC dispose maintenant d'outils et de modèles optimisés disponibles auprès de divers fournisseurs, et des atténuations de modélisation standard peuvent être appliquées. Bien qu'il existe des différences entre des outils comme LTSpice, PLECS et le SpeedFit 2.0 Design Simulator™ de Wolfspeed, les conseils des experts de Wolfspeed Power permettront d'obtenir une précision de simulation avec le SiC.

Simulation statique avec LTSpice

Les modèles Spice de Wolfspeed sont optimisés pour des températures comprises entre 25 ºC et 150 ºC. Le fonctionnement de la diode de corps est optimisé pour une tension de commande, VGS, de -4 V pour les dispositifs de 3ème génération et de -5 V pour ceux de 2ème génération. Les ingénieurs peuvent incorporer une capacité d'auto-échauffement et de thermique transitoire et une inductance parasite. Cependant, les effets bipolaires parasites et associés, le processus de multiplication des avalanches, et la variation de la tension d'allumage des diodes de corps avec porte à source ne sont pas modélisés.

Les résultats de la simulation statique de LTSpice - la courbe IV à différentes valeurs VGS et la courbe des diodes de corps - correspondent bien aux mesures réelles. Pour les capacités - capacité d'entrée, Ciss, capacité de sortie, Coss, et capacité de transfert inverse, Crss, également, les résultats de la simulation statique sont assez proches pour l'objectif. Les ingénieurs peuvent donc se fier aux paramètres statiques de la modélisation Spice.

Un test à double impulsion

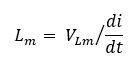

Un point de repère typique de caractérisation pour la compréhension du comportement dynamique est un test à double impulsion en demi-pont. Lorsqu'il est modélisé sans aucune considération, telle que la parasitique, la simulation est significativement hors des résultats mesurés (Figure 1). Dans la mesure où la consommation d'énergie a un impact sur l'efficacité, une différence aussi importante a un effet significatif sur les calculs thermiques.

Figure 1 : Les résultats idéaux de la simulation de la perte de commutation lors d'un test à double impulsion sont

environ 45 % de moins que celles de la fiche technique du DUT, U2.

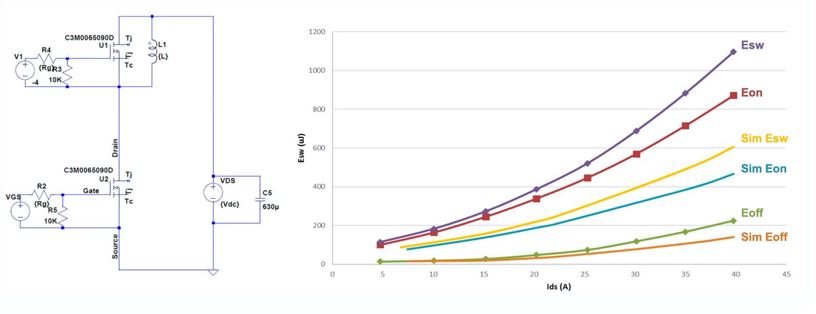

Dans le cas du test, une impulsion longue est suivie d'un écart de 1 µs, qui est suivi d'une impulsion courte. La mise en marche et l'arrêt sont mesurés de manière conventionnelle, comme pour les appareils à base de Si. Un examen plus approfondi des formes d'onde (Figure 2) met en évidence la différence entre les résultats réels et les résultats idéaux simulés. Les temps de montée et de descente dans la simulation sont beaucoup plus rapides que ceux mesurés car les résultats réels sont affectés par des inductances - inductance parasite, Lm, entre les deux dispositifs, et inductance du boîtier, Lpkg, qui est l'inductance source du boîtier. Il existe également une différence entre les résultats de dépassement pour la mise en marche et l'arrêt. Ces différences contribuent à la différence globale des pertes de commutation.

Figure 2 : Une comparaison des formes d'onde révèle que le temps de montée de commutation réel

est de 39 ns contre 22,83 ns simulés (temps beaucoup plus court) et que le

temps de descente est de 20 ns contre 13,63 ns simulés.

Pour obtenir un modèle précis, les inductances doivent être extraites et importées manuellement dans LTSpice. Le modèle thermique dans PLECS, en revanche, n'inclut pas les composants parasites.

Résultat Lm

|

Lm est l'inductance entre la source de l'appareil U1 côté haute tension

Où : Cela donne une valeur de 23,1674 nH pour Lm.

|

Figure 3 : Informations extraites de la forme d'onde réelle peut être utilisé pour calculer Lm. |

Qu'il s'agisse d'un buck synchrone, d'un boost synchrone, d'un demi-pont ou d'un pont complet, la conception utilise probablement une configuration de dispositifs haut et bas côté par l'intermédiaire d'un PCB. Si les bonnes pratiques de mise en œuvre sont respectées, Lm se situe dans la plage de 20 nH à 25 nH. Les ingénieurs peuvent considérer cela comme une règle empirique à utiliser dans les simulations.

Extraction de Lpkg

Les concepteurs peuvent s'attendre à ce que Lpkg soit le même pour tous les fournisseurs pour les boîtiers standard comme le TO-247. Cependant, il existe des variations dues aux différences d'épaisseur des cadres de connexion, de liaison des fils de source et de longueur de l'épaulement du boîtier. S'il est disponible dans une fiche technique, il peut facilement être branché sur le modèle. Sinon, il peut être extrait d'une forme d'onde mesurée et extrapolé à ce qui pourrait être une bonne estimation pour le boîtier en question.

Où :

VLpkg = Vds — VLds + Vdson = —11,515 V

Lds = 6,5372 nH du modèle Spice,

Vds = ~-27,8 V de la forme d'onde réelle,

VLds = -15,035 V,

Vds_on @ 20 A = 1,25 V de la fiche technique C3M0065090D et

di/dt = -2,3 x 109

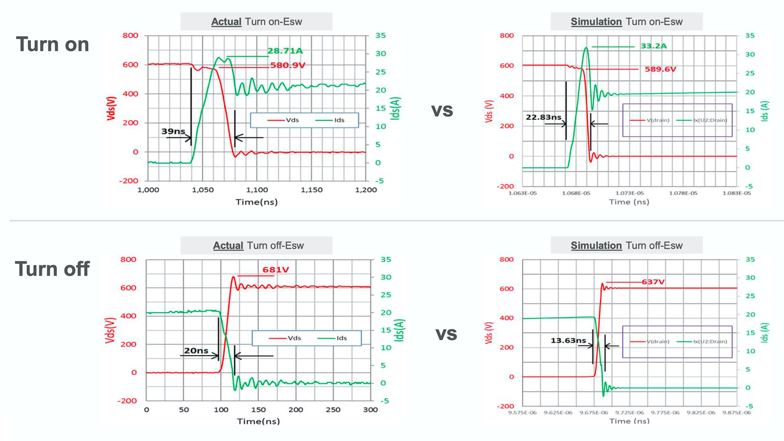

Figure 4 : L'ajout des inductances calculées dans le LTSpice

se rapproche des mesures réelles.

Dans notre exemple, cela donne une valeur Lpkg de 2,503 nH. Malgré les variations, cette valeur peut être considérée comme une bonne estimation et une règle empirique fiable. La simulation après prise en compte des inductances rend le modèle dynamique précis (Figure 4).

En tenant compte des inductances, l'énergie totale de commutation Esw ainsi que Eon et Eoff pour le test à double impulsion réel et simulé deviennent très proches (Figure 5).

Figure 5 : Après avoir utilisé les parasites de configuration, les

pertes de commutation correspondent à la fiche technique C3M0065090D.

En utilisant ces règles empiriques pour Lm et Lpkg, les ingénieurs peuvent obtenir des calculs de pertes et des calculs thermiques assez précis pour leur budget thermique.

MOSFETs parallélisés

Les MOSFET SiC sont souvent placés en parallèle pour augmenter la capacité de transport de courant ainsi que les niveaux de puissance. Cependant, il faut prendre en compte certaines considérations :

- •Déséquilibre de courant dû à la tension de seuil, VTH, différences

- • Déséquilibre actuel dû à des inductances parasites asymétriques

- • Oscillation de l'entraînement de la porte

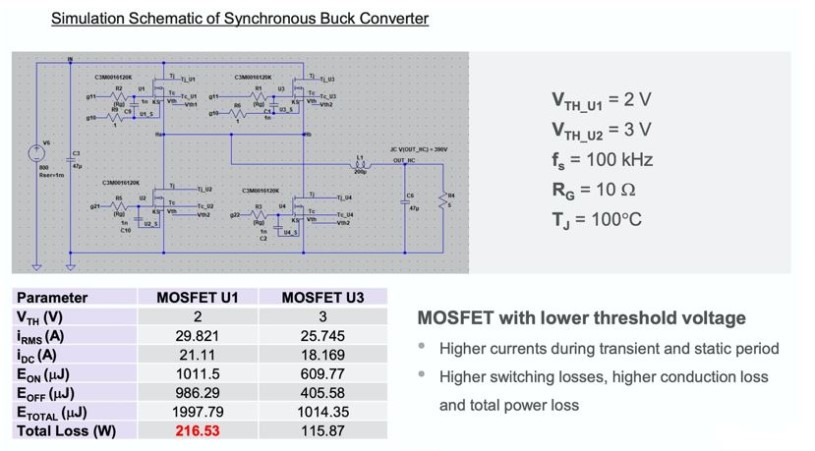

Avec les MOSFETs SiC Wolfspeed, il y a peu de risques que les caractéristiques des appareils ne correspondent pas. Cependant, les ingénieurs peuvent être amenés à utiliser d'autres pièces en SiC avec une tolérance de spécification plus large et peuvent choisir, par exemple, un dispositif avec 2 V VTH et un autre avec 3 V. Le dispositif avec le seuil inférieur a un transitoire plus élevé et, de ce fait, des pertes de commutation et de conduction plus élevées, donc des pertes totales de puissance plus élevées (Figure 6).

Figure 6 : Les pertes totales du dispositif de 2 V sont presque deux fois

plus élevées que celles de l'appareil à 3 V en raison du déséquilibre actuel.

Bien que les deux dispositifs aient la même résistance de grille, RG, et fonctionnent à la même température et à la même fréquence de commutation, la modélisation sans aucune considération fait que U1 a plus de 200 W de pertes totales et U3 un peu plus de 100 W. Les formes d'onde simulées montrent que U1 atteint un dépassement d'environ 70 A avant de tomber à un état stable de 50 A, tandis que U3 atteint un dépassement d'environ 49 A et se stabilise à 30 A. Il y a donc un décalage considérable dans la capacité de transport de courant entre les deux appareils ainsi que de légères différences dans les temps de mise en marche et d'arrêt.

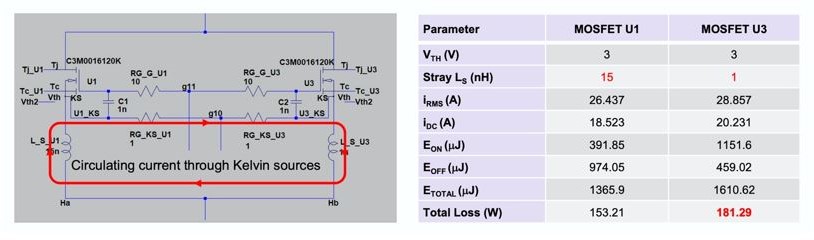

La deuxième cause de déséquilibre de courant est la parasitique asymétrique. Prenons le cas de deux dispositifs, U1 et U3 (Figure 7) de VTH identique mais avec des inductances de source différentes. Il en résulte un déséquilibre considérable des di/dt, des tensions entre les inductances parasites, des commandes de grille et des courants de drain. Les formes d'onde simulées montrent que le courant monte et descend beaucoup plus rapidement pour U3, et atteint des valeurs plus élevées pour IDC et IRMS, entraînant une perte de commutation plus élevée de 17,9 % et une perte totale plus élevée de 18,3 % dans ce MOSFET.

Figure 7 : La différence d'inductance parasite Ls pour U1

et U3 est exagéré dans cet exemple pour démontrer

l'impact de l'inadéquation.

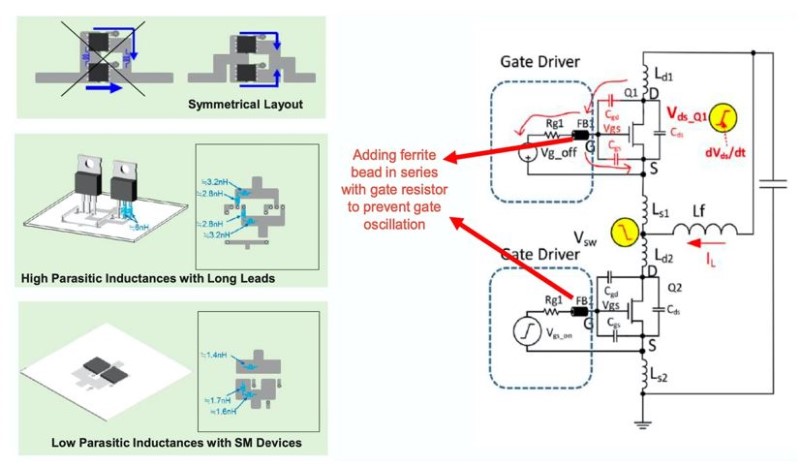

Atténuer l'inadéquation avec une bonne conception

L'impact des MOSFET mal appariés peut être considérablement réduit en incorporant de bonnes pratiques de conception. À titre d'exemple, prenons le nouveau modèle de référence CRD60DD12N du convertisseur solaire de 60 kW qui utilise deux MOSFET C3M075120K de 75 mΩ et 1 200 V en parallèle (Figure 8). L'utilisation de deux des MOSFET à 4 fils TO-247 ayant la VTH la plus élevée et la plus basse sur un échantillon de 60 pièces permet toujours d'obtenir un matériel qui fonctionne bien, si de bonnes pratiques de conception sont employées.

Figure 8 : Malgré la différence VTH, les effets

de l'inadéquation des appareils sont minimisés dans ce circuit de test.

La disposition symétrique des circuits imprimés est essentielle pour réduire le courant circulant dans les boucles de grille des interrupteurs en parallèle. Séparez la boucle d'alimentation de la boucle de la grille, prévoyez suffisamment d'amortissement pour empêcher l'oscillation de la grille, et ajoutez une perle de ferrite à la jambe de la grille pour réduire les pics de tension et le bourdonnement sur la grille qui peuvent endommager les pièces (Figure 9).

Figure 9 : De bonnes pratiques de conception - disposition symétrique serrée, signal équilibré

séparation des boucles d'alimentation et de grille, amortissement pour empêcher

l'oscillation de la grille, et petit RG avec une perle de ferrite,

permettent toutes de réduire le déséquilibre du courant.

Grâce à ces pratiques de conception, Q1 dans le circuit de test transporte 47,6 % du courant total, tandis que Q2 en transporte 52,4 %, ce qui permet d'obtenir des résultats acceptables dans le monde réel malgré l'inadéquation des appareils.

Élargir le choix des outils

Les conceptions à base de SiC peuvent être modélisées à l'aide de SpeedFit, LTSpice ou PLECS de Wolfspeed. Si SpeedFit et LTSpice peuvent être utilisés à titre gratuit en s'inscrivant à Wolfspeed, PLECS nécessite un abonnement. Les différences entre les outils affectent à la fois la manière de générer les simulations et leurs limites, comme le traitement des parasites et le calcul des pertes.