Ora più che mai, gli ingegneri stanno scegliendo prodotti basati sul carburo di silicio (SiC) per la loro maggiore efficienza, la densità di alimentazione e il migliore rapporto costo-efficacia complessivo del sistema rispetto ai componenti basati sul silicio (Si).

Al di là dei principi di progettazione di base comuni tra SiC e Si, e della necessità di tenere conto delle diverse caratteristiche, capacità e vantaggi di SiC, gli ingegneri devono modellare e simulare per garantire il raggiungimento degli obiettivi di progettazione.

Come per Si, SiC dispone ora di strumenti e modelli ottimizzati disponibili presso vari fornitori e possono essere applicate le attenuazioni standard di modellazione. Mentre ci sono differenze tra strumenti come LTSpice, PLECS e SpeedFit 2.0 Design Simulator™ di Wolfspeed, i suggerimenti degli esperti di Wolfspeed contribuiranno a raggiungere la precisione della simulazione con SiC.

Simulazione statica con LTSpice

I modelli Spice di Wolfspeed sono ottimizzati per 25ºC e 150ºC. Il funzionamento del diodo del corpo è ottimizzato per una tensione di azionamento, VGS, di -4 V per i dispositivi Gen. 3 e -5 V per i dispositivi Gen. 2. Gli ingegneri possono incorporare l'auto-riscaldamento e la capacità termica transitoria e l'induttanza parassitaria. Tuttavia, gli effetti bipolari parassitari e gli effetti associati, il processo di moltiplicazione delle valanghe e la variazione della tensione di accensione dei diodi corporei con gate-to-source non sono modellati.

I risultati della simulazione statica LTSpice - la curva IV a vari valori VGS e la curva a diodi corporei - corrispondono bene alle misurazioni reali. Per le capacitanze - capacitanza di ingresso, Ciss, capacitanze di uscita, Coss e capacitanze di trasferimento inversa, Crss, anche i risultati della simulazione statica sono abbastanza vicini allo scopo. Gli ingegneri possono quindi sentirsi sicuri dei parametri statici della modellazione Spice.

Un test a doppio impulso

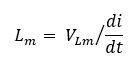

Un tipico punto di riferimento di caratterizzazione per la comprensione del comportamento dinamico è un test a doppio impulso a mezzo ponte. Se modellata senza alcuna considerazione, come ad esempio i parassiti, la simulazione è significativamente al di fuori dei risultati misurati (Figura 1). Poiché il consumo di energia ha un impatto sull'efficienza, una differenza così grande ha un effetto significativo sui calcoli termici.

Figura 1: I risultati ideali della prova di simulazione di commutazione a doppio impulso sono

circa il 45% inferiori rispetto a quelli della scheda tecnica per il DUT, U2.

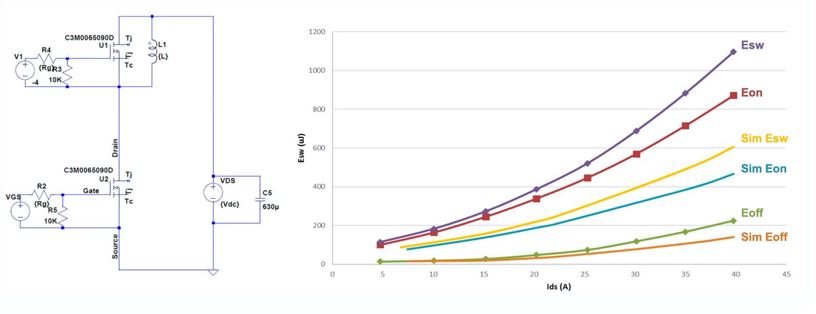

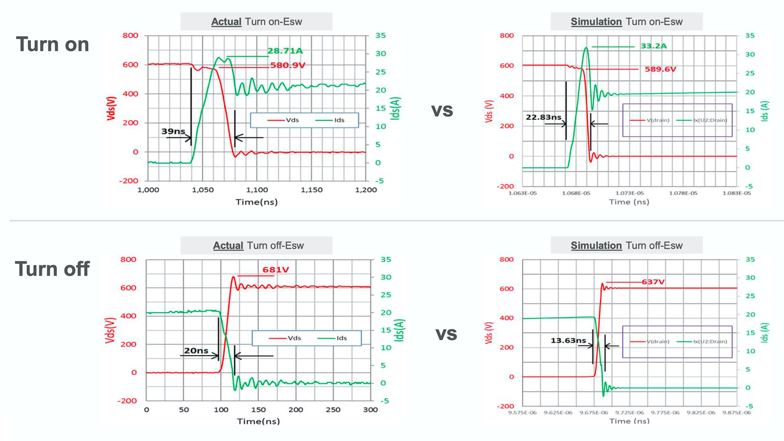

Nel caso del test, un impulso lungo è seguito da uno scarto di 1 µs, seguito da un impulso breve. L'accensione e lo spegnimento sono misurati nel modo convenzionale come si farebbe con i dispositivi basati sul Si. Guardando più da vicino le forme d'onda (Figura 2) appare in evidenza la differenza tra risultati simulati reali e ideali. Sia i tempi di salita che di discesa nella simulazione sono molto più veloci di quelli misurati perché i risultati effettivi sono influenzati dalle induttanze - induttanza parassita parassita, Lm, tra i due dispositivi, e induttanza del pacchetto, Lpkg, che è l'induttanza sorgente del pacchetto. C'è anche una differenza tra i risultati di superamento per l'accensione e lo spegnimento. Queste differenze contribuiscono alla differenza complessiva delle perdite di commutazione.

Figura 2: Un confronto delle forme d'onda rivela che il tempo di salita di accensione effettiva

è di 39 ns rispetto al più veloce 22,83 ns simulato, mentre l'effettivo

tempo di caduta è 20 ns rispetto a 13,63 ns, simulato.

Per ottenere un modello accurato, le induttanze devono essere estratte e importate manualmente in LTSpice. Il modello termico in PLECS, invece, non include componenti parassitari.

Rilevamento di Lm

|

Lm è l'induttanza tra la sorgente del dispositivo U1 high-

Dove: Questo restituisce un valore di 23,1674 nH per Lm.

|

Figura 3: Informazioni estratte dalla forma d'onda reale da utilizzare per calcolare Lm. |

Che si tratti di un buck sincrono, di un boost sincrono, di un half-bridge o di un full-bridge, il progetto probabilmente utilizza una configurazione di dispositivi high-side e low-side attraverso un PCB. Se si seguono buone pratiche di layout, Lm è compreso tra 20 nH e 25 nH. Gli ingegneri possono considerare questo come una regola generale da utilizzare nelle simulazioni.

Estrazione di Lpkg

I progettisti potrebbero aspettarsi che Lpkg sia lo stesso tra i fornitori per i pacchetti standard come il TO-247. Tuttavia, ci sono variazioni dovute alle differenze nello spessore dei telai in piombo, nell'incollaggio del filo sorgente e nella lunghezza della spalla sul pacchetto. Se disponibile in una scheda tecnica, si può facilmente inserire nel modello. In caso contrario, si può estrarre da una forma d'onda misurata ed estrapolare in quella che potrebbe essere una buona stima per il pacchetto in questione.

Dove:

VLpkg = Vds — VLds + Vdson = —11,515 V

Lds = 6.5372 nH dal modello Spice,

Vds = ~-27.8 V dalla forma d'onda reale,

VLds = -15,035 V,

Vds_on @ 20 A = 1,25 V dalla scheda tecnica di C3M0065090D e

di/dt = -2,3 x 109

Figura 4: L'aggiunta delle induttanze calcolate nel modello LTSpice

consente di avvicinarsi alle misurazioni effettive.

Nel nostro modello, questo restituisce un valore di Lpkg di 2,503 nH. Nonostante le variazioni, questo valore può essere preso come una buona stima e come un'affidabile regola empirica. La simulazione dopo aver preso in considerazione le induttanze rende il modello dinamico accurato (Figura 4).

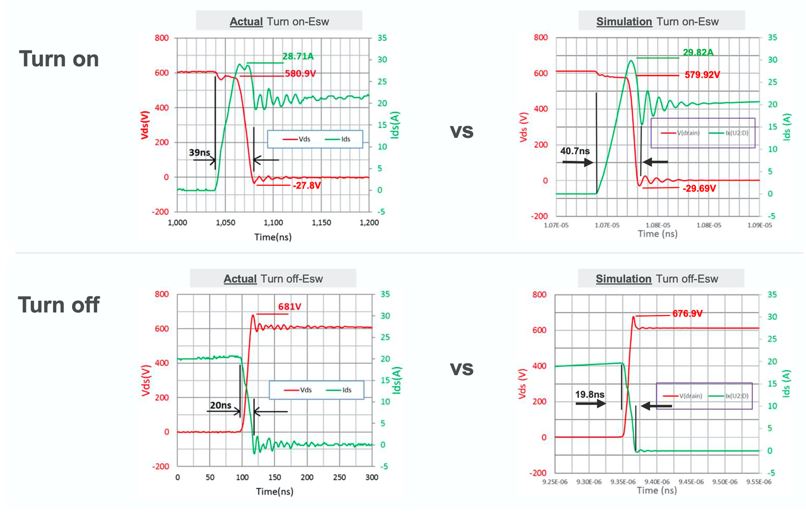

Considerate le induttanze, l'energia di commutazione totale Esw così come Eon ed Eoff per la prova a doppio impulso reale e simulata diventano molto vicine (Figura 5).

Figura 5: Dopo aver utilizzato i parassiti di configurazione, le perdite di commutazione simulate

corrispondono alla scheda tecnica del C3M0065090D.

Usando queste regole empiriche per Lm e Lpkg, gli ingegneri possono ottenere calcoli termici e di perdita abbastanza accurati per il loro budget termico.

MOSFET in parallelo

I MOSFET SiC sono spesso posizionati in parallelo per aumentare la capacità di trasporto della corrente e i livelli di alimentazione. Ci sono però alcune considerazioni da tenere a mente:

- • Sbilanciamento di corrente dovuto alla tensione di soglia, VTH, differenze

- • Sbilanciamento di corrente dovuto a induttanze parassitarie asimmetriche

- • Oscillazione del gate drive

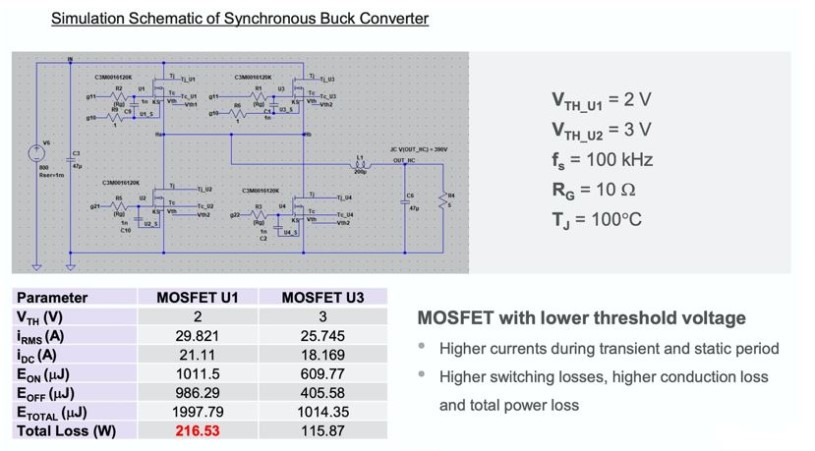

Con i MOSFET SiC Wolfspeed, ci sono poche possibilità che le caratteristiche del dispositivo non corrispondano. Tuttavia, agli ingegneri può essere richiesto di utilizzare altre parti SiC con una più ampia tolleranza di specifica e possono scegliere, ad esempio, un dispositivo con 2 V VTH e un altro con 3 V. Il dispositivo con la soglia inferiore ha un transitorio più alto e per questo motivo, maggiori perdite di commutazione e maggiori perdite di conduzione, quindi maggiori perdite di alimentazione totale (Figura 6).

Figura 6: Le perdite totali del dispositivo a 2 V sono quasi il doppio di quelle

del dispositivo a 3 V a causa dello squilibrio di corrente.

Anche se entrambi i dispositivi hanno la stessa resistenza del gate, RG, e funzionano alla stessa temperatura e frequenza di commutazione, la modellazione senza alcuna considerazione fa sì che U1 abbia perdite totali superiori a 200 W e U3 poco più di 100 W. Le forme d'onda simulate mostrano che U1 raggiunge picchi di circa 70 A prima di cadere allo stato stazionario di 50 A, mentre U3 raggiunge picchi di circa 49 A e si stabilizza allo stato stazionario di 30 A. Vi è quindi un notevole disallineamento nella capacità di trasporto della corrente tra i due dispositivi, oltre a leggere differenze nei tempi di accensione e spegnimento.

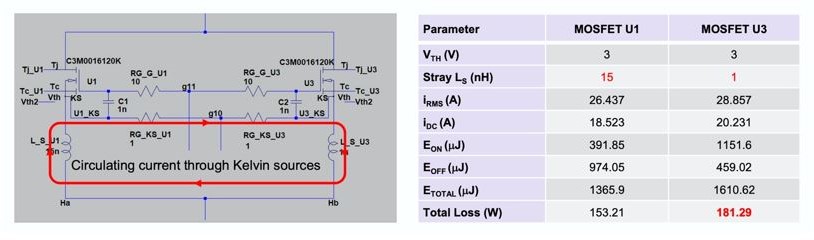

La seconda causa dello squilibrio attuale sono i parassiti asimmetrici. Prendiamo come esempio due dispositivi, U1 e U3 (Figura 7) che hanno lo stesso VTH ma induttanze sorgente diverse. Ciò causa un notevole squilibrio delle tensioni di/dt tra induttanze vaganti, azionamenti dei gate e correnti di drenaggio. Le forme d'onda simulate mostrano che la corrente sale e scende molto più velocemente per U3 e raggiunge valori più alti per IDC e IRMS, causando una perdita di commutazione superiore del 17,9% e una perdita totale del 18,3% in quel MOSFET.

Figura 7: La differenza nell'induttanza di dispersione Ls per U1

e U3 è esagerata in questo esempio per dimostrare

l'impatto del disallineamento.

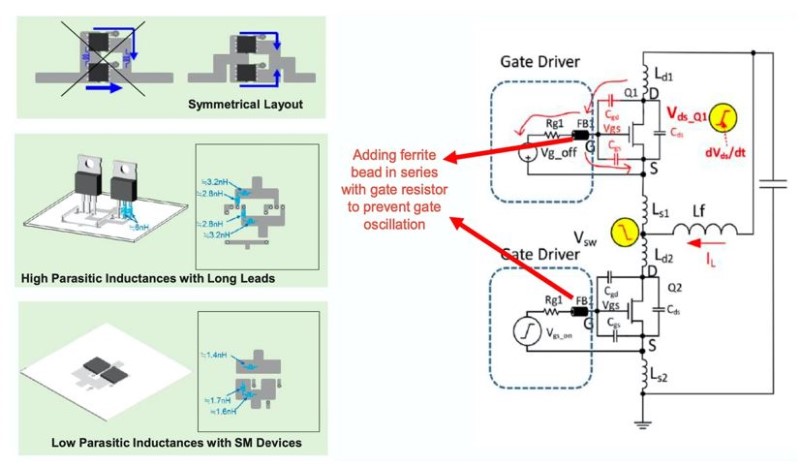

Mitigare il disallineamento con un buon design

L'impatto dei MOSFET non allineati può essere notevolmente ridotto incorporando buone pratiche di progettazione. A titolo di esempio, prendiamo il progetto di riferimento per l'inverter solare da 60 kW CRD60DDD12N che utilizza due MOSFET da 75 mΩ 1.200V C3M075120K in parallelo (Figura 8). Utilizzando due dei MOSFET a 4 conduttori TO-247 con il più alto e il più basso VTH da un campione di 60 parti si ottiene ancora un hardware che funziona bene, se si utilizzano buone pratiche di progettazione.

Figura 8: Nonostante la differenza di VTH, gli effetti

del disallineamento dei dispositivi sono minimizzati nel circuito di test.

Il layout simmetrico del PCB è fondamentale per ridurre la corrente di circolazione nei loop di gate degli interruttori in parallelo. Separare l'anello di alimentazione dall'anello del gate, fornire uno smorzamento sufficiente a prevenire le oscillazioni del gate e aggiungere un cordone di ferrite alla gamba del gate per ridurre i picchi di tensione e gli squilli sul gate che possono causare danni alle parti. (Figura 9).

Figura 9: Buone pratiche di progettazione - layout strettamente simmetrico, segnale equilibrato,

separazione dei loop di alimentazione e dei gate, smorzamento per evitare che

il gate oscilli, e RG piccolo con una perlina di ferrite per ridurre l'oscillazione,

tutto al fine di ridurre lo squilibrio di corrente.

A causa di queste pratiche di progettazione, il Q1 nel circuito di prova porta il 47,6% della corrente totale, mentre il Q2 porta il 52,4%, raggiungendo risultati accettabili nel mondo reale nonostante il disallineamento del dispositivo.

Aumento della scelta di strumenti

I progetti basati su SiC possono essere modellati utilizzando SpeedFit, LTSpice o PLECS di Wolfspeed. Mentre SpeedFit e LTSpice possono essere utilizzati liberamente registrandosi a Wolfspeed, PLECS viene fornito con un abbonamento a pagamento. Le differenze tra gli strumenti influiscono sia sul modo di generare simulazioni che sui loro limiti, come ad esempio nella gestione dei parassiti e nel calcolo delle perdite.