アルテラの低コストMAX® 10個のFPGAは、CPLDとFPGAの利点を1つのパッケージにまとめています。両方の長所を生かしたMAX 10 FPGAは、コスト効率の高い統合の次のレベルを実現します。クラウドに接続されたあらゆるスマート デバイスに最適なコアです。

高度な機能を搭載し、組み込み製品を効率的に実装できるように最適化されたMAX 10 FPGAは、使い方が簡単です。MAX 10アプリケーションの構築は、 アルテラの 多用途の開発キット、サンプル設計、強力なユーザー コミュニティ。

MAX 10 FPGAは、以下の機能によりコストとサイズを削減します。

-

- 内蔵フラッシュ ビット ストリームとユーザー データの不揮発性ストレージ用。

-

- 32ビット ニオス® IIソフトプロセッサ 別個のプロセッサが不要になります。

-

- リモートアップグレード機能 個別の構成コントローラが不要になります。

-

- 高度なクロック管理のための内部 PLL

-

- 単一電源 オプションにより、PCBボードの層数が削減され、複数のレギュレータの必要性が軽減されます。

-

- 統合された マルチチャンネル、12ビットSAR ADC により、外部アナログ-デジタル コンバータが不要になります。

-

- 内蔵の 温度検知ダイオード により、別個の 温度センサーが不要になります。

-

- 多用途のI/Oリング により、電圧レベル トランスレータと受動部品の要件が軽減されます。

MAX 10 FPGAの大きな利点は内部フラッシュ メモリであり、Alteraは内部フラッシュをさらに便利にする多くの機能を組み込んでいます。FPGAでは通常、外部メモリから構成イメージを読み取るために電源投入時間が必要です。MAX 10 FPGAは、動的なフェイルセーフ リモート アップグレードを提供する複数の内部構成フラッシュ アレイの1つから瞬時に電源を投入できる機能を備えています。ウォッチドッグ タイマーを有効にすると、リモート フラッシュ構成を監視し、構成が失敗した場合に自動的に以前のイメージに戻ることができます。さらに、複数の統合フラッシュ アレイがプログラムとデータのストレージを提供するため、多くのアプリケーションで外部の不揮発性メモリが不要になります。

-

MAX 10 FPGAには統合電圧レギュレータが組み込まれており、単一の3.0 - 3.3 V電源オプションにより電源コストとサイズが削減されます。高効率デュアル電源デバイス オプションも利用できます。多用途のI/Oリングは、3.3 V LVTTL/LVCMOSを含むさまざまなシングルおよび差動I/O規格をサポートします。独立したI/Oバンク電圧機能と組み合わせると、個別のレベル変換バッファを回避できます。すべてのI/O要素は、ノイズ耐性とスイッチのデバウンスを提供するために、オプションでシュミット トリガー入力バッファを構成できます。各I/O要素には、高速シリアル バスおよびメモリ インターフェイス用のDDRモードで動作できる2つの出力対応レジスタが含まれています。オプションの内部プルアップ抵抗を備えたオープンドレイン対応出力、設定可能なスルーレート制御、プログラム可能な電流強度により、一部のインターフェース規格では最大16 mAを駆動できます。 -

マルチチャンネルADC、温度検知ダイオード、統合型116 MHz内部リング発振器を含むアナログ ブロックがこの強力なアーキテクチャを完成させます。PWMまたはデルタ シグマ コンバータとAlteraのDSP Builderを組み合わせることで、ADC変換と信号処理を必要とする監視および制御アプリケーションの中核でMAX 10 FPGAを使用できます。TMSCの55 nm NORフラッシュ テクノロジー、Alteraの豊富な知的財産コレクション、強力な開発エコシステムにより、設計者はデバイスの柔軟なFPGAファブリックに簡単にアクセスできます。このファブリックには、DSPブロック、LPDDR2/DDR3インターフェイス機能、PLL、最大50Kのロジック エレメント (LE)、および1.6MビットのブロックRAMが組み込まれています。Alteraの使いやすいIPポートフォリオの中心となるのはQsysシステム統合ツールです。これにより、開発者は相互運用可能なさまざまなソフトコア モジュールをインスタンス化するシステム アーキテクチャを定義できます。

-

-

図1 Qsys開発環境 (拡大表示)

-

このポートフォリオには、世界で最も汎用性の高い組み込みプロセッサである32ビットNios IIプロセッサが含まれています。NIOS IIプロセッサは、高速コア、大規模なユーザー コミュニティ、包括的なオペレーティング システム サポートを備え、最大130MHzで動作できます。

図2: Nios IIプロセッサ アーキテクチャとOSサポート

開発キットですぐに始められます

開発キットは設計プロセスを簡素化し、十分に文書化されたリファレンス プラットフォーム上での迅速なFPGA設計開発と組み込みソフトウェアを可能にします。さまざまなキットが用意されており、幅広い用途に最適化されています。基盤となるハードウェア アーキテクチャを試行済みおよびテスト済みのリファレンス デザイン要素に基づいて構築すると、実用的なサンプル プロジェクトを開始点として使用できるため、開発がスピードアップし、リスクが軽減されます。この戦略を、開発キット固有のBSP、統合ネットワーク スタック、デバイス ドライバーを備えたさまざまなオペレーティング システムと組み合わせることで、開発時間を短縮できます。

Terasic Nios II組み込み開発キット (NEEK) には、完全なプロセッサ ベースのシステムを作成するために必要なものがすべて揃っています。これは、さまざまなアプリケーションに重点を置いた多数のリファレンス デザインを備えた統合プラットフォームです。このキットは、組み込み処理アプリケーション、マルチメディア インターフェイス製品、ヒューマン マシン インターフェイス、ビデオ ディスプレイ向けのカスタマイズされたソリューションを迅速に設計できるように最適化されています。このキットには、マルチタッチ ジェスチャをネイティブにサポートする静電容量式LCDマルチメディア カラー タッチ パネルが搭載されています。また、8メガピクセルの画像センサー、光センサー、3軸加速度計も搭載されています。デモのリファレンス デザインには、ロボット制御、HDMI Rx、センシング、オーディオ、カメラ インターフェイスが含まれます。

図3: Terasic MAX 10 Nios II組み込み開発キット

Altera MAX 10 FPGA開発キットは、HDMIや産業用イーサネット設計など、さまざまなアプリケーション向けに最適化されています。Nios IIプロセッサ用の組み込みLinuxリファレンス デザインが用意されており、強力なオンライン コミュニティ サポートが備わっています。開発キットには、HSMCとDigilent Pmodを使用したドーターカードと周辺機器へのインターフェースが含まれています。™ 互換性のあるコネクタを備え、電力モニタのグラフィカル ユーザー インターフェイス (GUI) を使用したFPGA電力監視が組み込まれています。このボードは、設計のベースとなる実証済みのプラットフォームとして、十分に文書化され、オープンで、再利用可能です。

図4: Altera MAX 10 FPGA開発キット

図5: Altera MAX 10 FPGA開発キットのアーキテクチャ

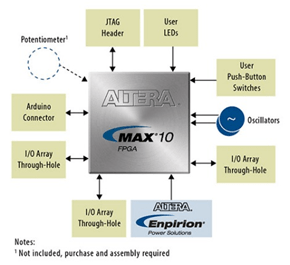

MAX 10 FPGA評価キットは、FPGA電源モニタリング機能と、レベル変換を可能にする調整可能なI/Oバンク電圧を統合した低コストのエントリー レベル ボードです。このボードにはAltera Enpiron電源が搭載されており、 FPGAのフラッシュ メモリ、ADCインターフェイス、デジタルI/Oリングに接続します。このキットは、互換性のあるArduinoシールドへの接続を可能にする統合型Arduino UNO R3インターフェース コネクタにより、非常に柔軟性に優れています。この機能により、次のような機能を備えた数千の周辺ボードが可能になります。 センサー、モーターコントローラー、GPS、無線トランシーバーなど。キットのPCBボードと回路図は十分に文書化されており、設計のモデルとして利用できます。

図6: MAX 10 FPGA評価ボード

図7: MAX 10 FPGA評価ボードのアーキテクチャ

Arrow社から提供されるBeMicro MAX 10開発キットを使用すると、設計者は組み込みアプリケーション向けにMAX 10 FPGAを評価し、利用することができます。これには、EnpironパワーSoC、8 MBのSDRAM、加速度計、LED、プッシュボタン、 および拡張接続が含まれています。拡張ヘッダーには、2つの6ピンDigilent Pmod™ コネクタと2つの4ピン プロトタイピング ヘッダー、および80ピン カード エッジ コネクタが含まれています。ユーザーは、内蔵のUSB-Blasterポートを介して開発ツールを直接インターフェースできます。このボードには、設計を加速するための入門ユーザー ガイドが十分に文書化されており、迅速な開発に最適な低コストのプロトタイピング プラットフォームです。

図8: BeMicro MAX 10

図9: BeMicro MAX 10アーキテクチャ

関連商品を見る

Arrowの小型DECA MAX 10開発ボードは、強力で汎用性が高く、堅牢な開発プラットフォームです。DDR3メモリ、イーサネット、ジェスチャー光センサー、HDMI TX、オーディオ ライン入力または出力、microSDソケット、およびMAX 10 ADC用の2つのSMA入力が組み込まれています。DECAシステムには、ボードの2つの46ピンBeagle Bone Black (BBB) 拡張ヘッダーに接続するBYDカメラとWiFi-BLEワイヤレス インターフェイス モジュールが付属しています。開発者は、Texas InstrumentのBLEおよびWi-Fiソリューション ファミリを紹介するArrowのBLE/WIFI BeagleBone互換ケープを使用できます。開発者は、カメラ モジュールを使用して、MIPIビデオ入力インターフェイスで8メガピクセルのCMOS画像をキャプチャすることもできます。

図10: DECA MAX 10開発ボード

今すぐお試しください!

組み込みFPGAに基づくシステムの開発は、これまでになく簡単になりました。MAX 10 FPGAは、大幅なコスト削減を真に実現する統合レベルを提供します。オペレーティング システムBSPをサポートし、センシングやネットワーク接続用の周辺機器拡張にアクセスできるさまざまな開発キットにより、以前はより複雑で高価なマイクロコントローラを必要としていたアプリケーションでもMAX 10 FPGAを使用できるようになります。ウォッチドッグとフェイルセーフフォールバックを備えたUARTインターフェイスを介した動的イメージとユーザーフラッシュのアップロードの導入により、アップグレードとサポートが容易になり、将来を見据えた設計が可能になります。ハードウェア開発のリスクは、十分に文書化された堅牢なソリューションによって軽減され、ソフトウェアはリファレンス デザインと強力なユーザー コミュニティによって加速されます。FPGA設計ツールには、無料のWebベースのオプションも含まれています。AlteraのEclipseベースのソフトウェア開発環境を使用すると、ソフトウェアの開発とデバッグが容易になります。今すぐ始める方法については、Alteraの担当者にお問い合わせください。