Le economiche FPGA MAX® 10 della Altera offrono i vantaggi di CPLD e FPGA in una singola confezione. Basandosi sul meglio di entrambi i mondi, le FPGA MAX 10 offrono il livello successivo di economicità dell’integrazione, il core perfetto per qualsiasi dispositivo intelligente connesso al cloud.

Le FPGA MAX 10 sono semplici da usare e offrono moltissime caratteristiche sofisticate e sono ottimizzate per implementare prodotti integrati. La creazione di un’applicazione MAX 10 è semplice grazie ai kit di sviluppo versatili, ai progetti di esempio e alla sviluppata community di utenti della Altera.

Le FPGA MAX 10 riducono costi e dimensioni con:

-

- Flash interna: per la memorizzazione non volatile di bit stream dati utente.

-

- Processore softcore Nios® II a 32 bit: elimina la necessità di un processore separato.

-

- Capacità di aggiornamento remoto: eliminano la necessità di un controller di configurazione separato.

-

- PLL interni: per una gestione del clock avanzata.

-

- Opzione per singolo alimentatore: consente di ridurre i livelli della scheda PCB e la necessità per più regolatori.

-

- ADC SAT a 12 bit multicanale integrato: elimina la necessità di un convertitore esterno da analogico a digitale.

-

- Diodo di rilevamento della temperatura integrato: elimina la necessità di un sensore di temperatura separato.

-

- Anello I/O versatile: riduce i requisiti per traduzioni di livello delle tensioni e componenti passivi.

Un vantaggio significativo per le FPGA MAX 10 è rappresentato dalla memoria flash e la Altera ha incluso diverse caratteristiche che la rendono ancora più utile. Le FPGA richiedono generalmente del tempo all’accensione per leggere l’immagine di configurazione dalla memoria esterna. Le FPGA MAX 10 offrono un’accensione istantanea da uno dei diversi array di configurazione flash interni che forniscono un aggiornamento remoto dinamico a prova di errore. Un timer watchdog può essere abilitato per monitorare la configurazione remota della flash con un fall-back automatico a un’immagine precedente se la configurazione non riesce. Inoltre, più array flash integrati offrono archiviazione per programmi e dati, eliminando la necessità per memoria esterna e non volatile per molte applicazioni.

-

Le FPGA MAX 10 incorporano un regolatore di tensione integrato, che riduce il costo e le dimensioni dell’alimentatore con una singola opzione di alimentazione da 3 a 3,3 V. È anche disponibile un’opzione per dispositivo a doppia alimentazione ad alta efficienza. L’anello I/O versatile supporta diversi standard I/O singoli e differenziali, compresi LVTTL/LVCMOS a 3,3 V. Quando combinato con una capacità di tensione del banco I/O indipendente, è possibile evitare i buffer di traduzione di livelli separati. Ogni elemento I/O può essere configurato alternativamente come buffer di ingresso del trigger Schmitt per offrire immunità al rumore e antirimbalzo in commutazione. Ciascun elemento I/O contiene due registri abilitati in uscita che possono funzionare in modalità DDR con bus seriale ad alta velocità e interfacce di memoria. Le uscite a collettore aperto con resistenze di pull-up interne opzionali con controllo della velocità di variazione e potenza della corrente programmabile, possono pilotare fino a 16 mA per alcuni standard di interfaccia. -

Questa potente architettura è completata da blocchi analogici che contengono ADC multicanale, un diodo di rilevamento della temperatura e un oscillatore ad anello interno da 116 MHz. Combinato con un convertitore PWM o delta sigma e DSP Builder della Altera, le FPGA MAX 10 possono essere utilizzate come fulcro in applicazioni di monitoraggio e controllo che richiedono la conversione ADC e l’elaborazione dei segnali. Grazie alla tecnologia flash NOR da 55 nm della TMSC, alla raccolta avanzata della Altera di proprietà intellettuali e al potente ecosistema di sviluppo, i progettisti possono accedere alla struttura flessibile FPGA del dispositivo. Questa struttura comprende blocchi DSP, capacità di interfaccia LPDDR2/DDR3, PLL, fino a 50 K di elementi logici (LE) e 1,6 Mbit di RAM in blocco. Lo strumento di integrazione di sistema Qsys, di importanza centrale nel portfolio di proprietà intellettuali di facile utilizzo della Altera, consente agli sviluppatori di definire un’architettura di sistema che crea istanze per un’ampia varietà di moduli softcore interoperabili.

-

-

Figura 1: Ambiente di sviluppo Qsys (Ingrandisci)

-

Questo portfolio comprende il processore integrato con una delle maggiori versatilità al mondo, il processore Nios II a 32 bit. Il processore NIOS II può funzionare fino a 130 MHz per il core più veloce, e offre una grande comunità di utenti e un supporto completo per il sistema operativo.

Figura 2: Architettura e supporto per sistema operativo del processore Nios II

Inizia subito con un kit di sviluppo

I kit di sviluppo semplificano il processo di progettazione, consentendo lo sviluppo rapido di progetti basati su FPGA e software integrato su una piattaforma di riferimento ben documentata. Sono disponibili diversi kit, ottimizzati per una vasta gamma di applicazioni. Basando un’architettura hardware di base su elementi di un progetto di riferimento comprovati, si possono utilizzare progetti di esempio funzionanti come punto di partenza per velocizzare lo sviluppo e mitigare i rischi. Velocizza i tempi di sviluppo combinando questa strategia con l’ampia gamma di sistemi operativi disponibili con i BSP specifici al kit di sviluppo, stack di rete integrati e driver per dispositivi.

Il kit di sviluppo integrato Terasic Nios II (NEEK) offre tutto il necessario per creare un sistema completo basato su processore. Si tratta di una piattaforma integrata con diversi progetti di riferimento incentrati su una gamma di applicazioni. Il kit è ottimizzato per consentire la progettazione rapida di soluzioni personalizzate per applicazioni di elaborazione integrate, prodotti di interfaccia multimediali, interfacce uomo-macchina e display video. Il kit offre un pannello capacitivo a sfioramento a colori multimediale LCD con supporto nativo per i gesti multi-touch. Comprende anche un sensore di immagine a otto megapixel, un sensore di luce e un accelerometro a tre assi. I progetti di riferimento dimostrativi comprendono il controllo robotico, Rx HDMI, rilevamento, audio e interfacciamento con telecamera.

Figura 3: Kit di sviluppo integrato Terasic MAX 10 Nios II

Il kit di sviluppo Altera MAX 10 FPGA è ottimizzato per un’ampia gamma di applicazioni compresi progetti HDMI e Ethernet industriali. Per il processore Nios II è disponibile un progetto di riferimento Linux integrato e offre un grande supporto dalla community online. Il kit di sviluppo comprende interfacce a schede secondarie e periferiche utilizzando connettori compatibili con HSMC e Digilent Pmod™ e dispone del monitoraggio di potenza FPGA integrato utilizzando l’interfaccia grafica (GUI) per il monitor di potenza. La scheda è ben documentata, aperta e riutilizzabile come piattaforma comprovata su cui basare un progetto.

Figura 4: Kit di sviluppo Altera MAX 10 FPGA

Figura 5: Architettura del kit di sviluppo Altera MAX 10 FPGA

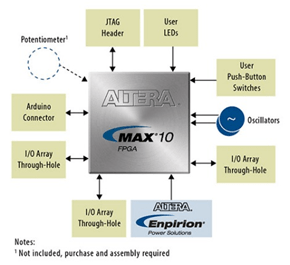

Il kit di valutazione MAX 10 FPGA è una scheda entry level economica con monitoraggio dell’alimentatore FPGA integrato e una tensione del banco I/O regolabile per consentire la traduzione di livello. La scheda contiene un alimentatore Altera Enpiron e consente l’accesso alla memoria flash della FPGA, alle interfacce ADC e all’anello I/O digitale. Il kit è estremamente flessibile grazie al connettore di interfaccia integrato per Arduino UNO R3 che consente la connessione a schede impilabili (shield) Arduino compatibili. Questa caratteristica consente di utilizzare migliaia di schede periferiche contenenti funzionalità quali sensori, controller di motori, GPS e ricetrasmettitori wireless. La scheda PCB e gli schemi del kit sono ben documentati e disponibile come modello per i progetti.

Figura 6: Scheda di valutazione MAX 10 FPGA

Figura 7: Architettura della scheda di valutazione MAX 10 FPGA

Il kit di sviluppo BeMicro MAX 10, disponibile dalla Arrow, consente ai progettisti di valutare e utilizzare la FPGA MAX 10 per le applicazioni integrate. Comprende un SoC di potenza Enpiron, 8 Mbyte di SDRAM, accelerometro, LED, pulsanti e connettività di espansione. I contatti di espansione comprendono due connettori a 6 pin Digilent Pmod™ e due contatti per prototipazione a 4 pin insieme a un connettore a filo scheda da 80 pin. Gli utenti possono interfacciare direttamente gli strumenti di sviluppo tramite la porta USB-Blaster incorporata. La scheda è ben documentata con una guida introduttiva per velocizzare i progetti e rappresenta una piattaforma ideale per la prototipazione a basso costo per lo sviluppo rapido.

Figura 8: BeMicro MAX 10

Figura 9: Architettura BeMicro MAX 10

La scheda di sviluppo dalle dimensioni ridotte DECA MAX 10 della Arrow è una piattaforma di sviluppo estremamente versatile e affidabile. Comprende memoria DDR3, Ethernet, sensori di luce per il riconoscimento di gesti, TX HDMI, ingresso o uscita audio, zoccolo microSD e due ingressi SMA per gli ADC MAX 10. Il sistema DECA è fornito completo con una telecamera BYD e moduli di interfaccia wireless WiFi-BLE che si connettono ai due contatti di espansione a 46 pin Beagle Bone Black (BBB). Gli sviluppatori possono utilizzare una scheda compatibile BLE/WIFI BeagleBone della Arrow che offre le famiglie delle soluzioni BLE e Wi-Fi della Texas Instrument. Gli sviluppatori possono utilizzare la telecamera per acquisire immagini CMOS a 8 megapixel con un’interfaccia di ingresso video MIPI.

Figura 10: Scheda di sviluppo DECA MAX 10

Provala subito.

Lo sviluppo di un sistema basato su una FPGA integrata non è mai stato così semplice. Le FPGA MAX 10 offrono livelli di integrazione che consentono veramente di contenere i costi. La varietà di kit di sviluppo con il supporto per sistema operativo BSP e l’accesso all’espansione delle periferiche per la connettività di sensori e rete, consente di utilizzare le FPGA MAX 10 in applicazioni che precedentemente richiedevano microcontroller complessi e costosi. L’introduzione del caricamento di immagini dinamiche e l’esecuzione del flash utente tramite interfaccia UART con watchdog e fall-back in caso di errore, rendono a prova di futuro i progetti, facilitando gli aggiornamenti e il supporto. Il rischio dello sviluppo dell’hardware è mitigato grazie alle soluzioni affidabili documentate e la creazione di software è velocizzata con progetti di riferimento e una community di utenti molto attiva. Gli strumenti progettuali FPGA comprendono anche opzioni basate su Web. Lo sviluppo e il debug del software è semplice con l’ambiente di sviluppo software basato su Eclipse della Altera. Contatta un rappresentante della Altera per informazioni su come iniziare subito.