Les FPGA MAX® 10 à bas coût d’Altera combinent les avantages des CPLD et des FPGA dans une seule solution. Offrant le meilleur des deux mondes, les FPGA MAX 10 permettent de passer au niveau supérieur de l’intégration économique. Ils représentent le cœur idéal pour tout appareil intelligent connecté au Cloud.

Dotés de nombreuses fonctions sophistiquées et optimisés pour mettre en œuvre efficacement les produits intégrés, les FPGA MAX 10 sont faciles à utiliser. Les kits de développement polyvalents, les exemples de conception et la solide communauté d’utilisateurs d’Altera facilitent la création d’une application MAX 10.

Les FPGA MAX 10 réduisent les coûts et la taille grâce aux caractéristiques suivantes :

-

- Mémoire Flash interne pour le stockage non volatile du flux binaire et des données des utilisateurs.

-

- Un processeur softcore Nios® II 32 bits élimine le besoin d’un processeur séparé.

-

- La capacité de mise à niveau à distance élimine le besoin d’un contrôleur de configuration séparé.

-

- PLL internes pour une gestion d’horloge sophistiquée.

-

- Une option d’alimentation électrique unique réduit les couches de cartes PCB et le besoin de plusieurs régulateurs.

-

- Un ADC SAR 12 bits multicanal intégré élimine le besoin d’un convertisseur analogique-numérique externe.

-

- Une diode de captage de température intégrée élimine le besoin d’un capteur de température séparé.

-

- Un anneau d’E/S polyvalent réduit le besoin d’un convertisseur de niveau de tension et de composants passifs.

L’un des principaux avantages des FPGA MAX 10 est leur mémoire Flash interne. Altera les a également dotés de plusieurs fonctions qui rendent la mémoire Flash interne encore plus puissante. Les FPGA nécessitent généralement un délai de démarrage pour lire l’image de la configuration de la mémoire externe. Les FPGA MAX 10 peuvent démarrer instantanément à partir de l’une des matrices Flash à configuration interne, qui fournit une mise à niveau à distance sécurisée dynamique. Vous pouvez activer un minuteur de boîte noire pour surveiller la configuration Flash distante avec basculement automatique vers une image antérieure en cas d’échec de la configuration. En outre, plusieurs matrices Flash intégrées assurent le stockage des programmes et des données, éliminant ainsi le besoin d’une mémoire non volatile externe dans de nombreuses applications.

-

Les FPGA MAX 10 possèdent un régulateur de tension intégré, qui réduit le coût de l’alimentation électrique et la taille avec une seule option d’alimentation électrique 3,0 - 3,3 V. Une option de double alimentation extrêmement efficace est également disponible. L’anneau d’E/S polyvalent prend en charge une grande variété de standards d’E/S uniques et différentielles, notamment 3.3-V LVTTL/LVCMOS. En le combinant avec la capacité de tension de la banque d’E/S indépendante, vous pouvez éviter les tampons de conversion de niveau séparés. En option, tous les éléments d’E/S peuvent configurer un tampon d’entrée de bascule de Schmitt pour fournir une immunité au bruit et un antirebond de commutateur. Chaque élément d’E/S contient deux registres à sortie activée pouvant fonctionner en mode DDR pour les interfaces de bus et de mémoire série à haut débit. Des sorties capables de prendre en charge le drainage ouvert avec des résistances de rappel internes en option, avec contrôle configurable de la vitesse de balayage et intensité du courant programmable, peuvent piloter jusqu’à 16 mA pour certains standards d’interface. -

Des blocs analogiques contenant des ADC multicanaux, une diode de captage de température et un oscillateur à anneau interne de 116 MHz intégré complètent cette puissante architecture. En les combinant avec un PWM ou des convertisseurs delta sigma et la solution DSP Builder d’Altera, vous pouvez utiliser les FPGA MAX 10 au cœur des applications de surveillance et de contrôle nécessitant une conversion ADC et un traitement du signal. Avec la technologie Flash NOR 55 nm de TMSC, la riche collection de propriété intellectuelle d’Altera et un puissant écosystème de développement, les concepteurs disposent d’un accès instantané à la matrice FPGA flexible de l’appareil. Cette matrice incorpore des blocs DSP, une capacité d’interface LPDDR2/DDR3, des PLL, jusqu’à 50 000 éléments logiques et 1,6 Mbit de RAM de bloc. L’outil d’intégration système Qsys se trouve au cœur du portefeuille de propriété intellectuelle facile à utiliser d’Altera. Cet outil permet aux développeurs de définir une architecture système qui instancie une grande variété de modules softcore interopérables.

-

-

Figure 1 : environnement de développement Qsys (vue agrandie)

-

Ce portefeuille inclut le processeur intégré le plus polyvalent au monde : le processeur Nios II 32 bits. Le processeur NIOS II peut fonctionner à 130 MHz maximum pour le cœur rapide, possède une vaste communauté d’utilisateurs et offre une prise en charge complète des systèmes d’exploitation.

Figure 2 : architecture du processeur Nios II et systèmes d’exploitation pris en charge

Démarrez immédiatement avec un kit de développement

Les kits de développement simplifient le processus de conception en permettant un développement rapide de la conception FPGA et en offrant un logiciel intégré sur une plate-forme de référence bien documentée. De nombreux kits sont disponibles et optimisés pour une large gamme d’applications. En basant une architecture matérielle sous-jacente sur des éléments de conception de référence testés et approuvés, vous pouvez utiliser des exemples de projets fonctionnels comme point de départ pour accélérer le développement et limiter les risques. Avec les BSP spécifiques au kit de développement, les piles de mise en réseau intégrée et les pilotes de périphérique, réduisez vos délais de développement en combinant cette stratégie avec une grande variété de systèmes d’exploitation disponibles.

Le kit de développement intégré Nios II (NEEK, Nios II Embedded Development Kit) de Terasic réunit tous les éléments requis pour créer un système basé sur un processeur complet. Il s’agit d’une plate-forme intégrée avec plusieurs conceptions de référence axée sur une gamme d’applications. Ce kit est optimisé pour permettre la conception rapide de solutions personnalisées pour les applications de traitement intégrées, les produits d’interface multimédia, les interfaces homme-machine et l’affichage vidéo. Il comprend un panneau tactile couleur multimédia LCD capacitif avec une prise en charge native des gestes multipoints. Il intègre également un capteur d’image de huit mégapixels, un capteur de lumière et un accéléromètre à trois axes. Les conceptions de référence de démonstration incluent le contrôle robotique, HDMI Rx, la détection, l’audio et l’interfaçage de la caméra.

Figure 3 : kit de développement intégré Nios II MAX 10 de Terasic

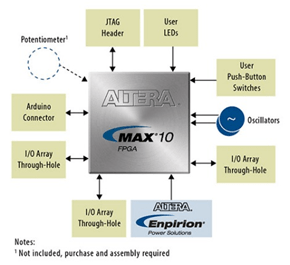

Le kit de développement FPGA MAX 10 d’Altera est optimisé pour une grande variété d’applications, y compris les conceptions HDMI et Ethernet industrielles. Une conception de référence Linux intégrée est disponible pour le processeur Nios II et inclut la prise en charge d’une solide communauté en ligne. Ce kit de développement inclut des interfaces avec des cartes filles et des périphériques qui utilisent des connecteurs compatibles HSMC et Digilent Pmod™, et permet de surveiller l’alimentation FPGA intégrée via une interface utilisateur graphique de surveillance de l’alimentation. La carte est bien documentée, ouverte et réutilisable en tant que plate-forme éprouvée sur laquelle baser une conception.

Figure 4 : kit de développement FPGA MAX 10 d’Altera

Figure 5 : architecture du kit de développement FPGA MAX 10 d’Altera

Le kit d’évaluation FPGA MAX 10 est une carte d’entrée de gamme à bas coût avec surveillance de l’alimentation électrique FPGA intégrée et une tension de banque d’E/S réglable pour permettre la conversion de niveau. La carte comprend une alimentation électrique Altera Enpiron et permet d’accéder à la mémoire Flash, aux interfaces ADC et à l’anneau d’E/S numérique du FPGA. Ce kit est incroyablement flexible grâce à un connecteur d’interface Arduino UNO R3 intégré qui permet la connexion à une solution Arduino Shields compatible. Cette fonction permet d’activer des milliers de cartes de périphérique contenant des fonctionnalités telles que des capteurs, des contrôleurs de moteur, des GPS et des transmetteurs sans fil. La carte PCB et les schémas du kit sont bien documentés et disponibles comme modèle pour les conceptions.

Figure 6 : carte d’évaluation FPGA MAX 10

Figure 7 : architecture de la carte d’évaluation FPGA MAX 10

Le kit de développement BeMicro MAX 10 disponible auprès d’Arrow permet aux concepteurs d’évaluer et d’utiliser le FPGA MAX 10 pour les applications intégrées. Il inclut un SoC d’alimentation Enpiron, 8 Mo de SDRAM, un accéléromètre, des DEL, des boutons poussoirs et une connectivité d’extension. Les embases d’extension comprennent deux connecteurs Digilent Pmod™ à 6 broches et deux embases de prototypage à 4 broches, ainsi qu’un connecteur de bord de carte à 80 broches. Les utilisateurs peuvent directement interfacer les outils de développement via le port USB-Blaster intégré. La carte est bien documentée avec un guide utilisateur de démarrage pour accélérer les conceptions et constitue une plate-forme de prototypage à bas coût parfaite pour le développement rapide.

Figure 8 : BeMicro MAX 10

Figure 9 : architecture BeMicro MAX 10

La petite carte de développement DECA MAX 10 d’Arrow est une plate-forme de développement puissante, extrêmement polyvalente et robuste. Elle intègre une mémoire DDR3, Ethernet, la détection de la lumière par mouvement, HDMI TX, une entrée ou sortie de ligne audio, une prise microSD et deux entrées SMA pour les ADC MAX 10. Le système DECA est fourni avec une caméra BYD et des modules d’interface sans fil WiFi-BLE qui se branchent dans les deux embases d’extension Beagle Bone Black (BBB) à 46 broches de la carte. Les développeurs peuvent utiliser la carte complémentaire compatible BLE/WIFI BeagleBone d’Arrow, qui prend en charge les gammes de solutions BLE et Wi-Fi de Texas Instruments. Les développeurs peuvent également utiliser le module de caméra pour capturer des images CMOS de 8 mégapixels à l’aide d’une interface d’entrée vidéo MIPI.

Figure 10 : carte de développement DECA MAX 10

Essayez dès aujourd’hui !

Le développement d’un système basé sur un FPGA intégré n’a jamais été aussi simple. Les FPGA MAX 10 offrent des niveaux d’intégration qui permettent de réaliser d’importantes économies. Divers kits de développement offrant la prise en charge des BSP de système d’exploitation et l’accès à l’extension périphérique pour la détection et la connectivité réseau permettent d’utiliser des FPGA MAX 10 dans des applications qui nécessitaient auparavant des microcontrôleurs plus complexes et coûteux. L’introduction du chargement Flash dynamique d’images et d’utilisateurs via une interface UART avec une boîte noire et un basculement sécurisé pérennise les conceptions en facilitant les mises à niveau et la prise en charge. Des solutions robustes et bien documentées limitent les risques liés au développement matériel, et des conceptions de référence et une solide communauté d’utilisateurs accélèrent les logiciels. Les outils de conception de FPGA incluent également des options Web gratuites. L’environnement de développement logiciel basé sur la solution Eclipse d’Altera simplifie le développement et le débogage des logiciels. Contactez un représentant d’Altera pour découvrir comment démarrer dès aujourd’hui !