Las FPGA MAX® 10 de bajo costo de Altera reúnen las ventajas de los CPLD y las FPGA en un solo paquete. Fundadas en lo mejor de ambos mundos, las FPGA MAX 10 ofrecen el siguiente nivel de integración rentable: el núcleo perfecto para cualquier dispositivo inteligente conectado con la nube.

Equipadas con características sofisticadas y optimizadas para implementar productos integrados de manera eficaz, las FPGA MAX 10 son fáciles de usar. Es muy fácil crear una aplicación MAX 10 gracias a los kits de desarrollo versátiles, los diseños de muestra y la sólida comunidad de usuarios de Altera .

Las FPGA MAX 10 reducen el costo y el tamaño con lo siguiente:

-

- Flash interno para el almacenamiento no volátil de flujo de bits y datos de usuario.

-

- Un procesador softcore Nios® II de 32 bit que elimina la necesidad de un procesador independiente.

-

- La capacidad de actualización remota que elimina la necesidad de contar con un controlador de configuración independiente.

-

- PLL internos para una administración sofisticada del reloj.

-

- Una sola opción de suministro de energía que reduce las capas del tablero PCB y la necesidad de contar con varios reguladores.

-

- Un ADC SAR multicanal de 12 bit integrado que elimina el requisito de contar con un conversor de análogo a digital externo.

-

- Un diodo de detección de temperatura que elimina la necesidad de contar con un sensor de temperatura independiente.

-

- Un anillo de E/S versátil que reduce los requisitos del traductor de nivel de tensión y de los componentes pasivos.

Una ventaja significativa de las FPGA MAX 10 es la memoria Flash interna. Además, Altera incluyó una serie de características que hacen que la memoria Flash interna sea aún más útil. Las FPGA generalmente requieren tiempo de encendido para leer la imagen de configuración de la memoria externa. Las FPGA MAX 10 presentan un encendido al instante de una de las muchas matrices Flash internas de configuración que proporcionan actualización remota dinámica a prueba de fallas. Puede habilitar un temporizador de vigilancia para controlar la configuración Flash remota con retroceso automático a la imagen anterior si la configuración no es correcta. Además, las matrices Flash múltiples e integradas proporcionan almacenamiento de programas y datos, por lo que eliminan la necesidad de contar con memoria externa, no volátil en muchas aplicaciones.

-

Las FPGA MAX 10 incorporan un regulador de tensión integrado que reduce el tamaño y el costo de suministro de energía con una sola opción de suministro de 3.0 a 3.3 V. También hay disponible una opción de dispositivo con suministro doble de alta eficiencia. El versátil anillo de E/S admite una variedad de estándares de E/S simples y diferenciales, incluidos los LVTTL/LVCMOS de 3.3 V. Cuando se combina con la capacidad de tensión de banco de E/S independiente, puede evitar búferes de traslación de nivel independientes. Cada elemento de E/S puede configurar opcionalmente un búfer de entrada de disparador Schmitt para proporcionar inmunidad al ruido y eliminar el rebote de interruptores. Cada elemento de E/S contiene dos registros de salida habilitados que pueden funcionar en el modo DDR para interfaces de memoria y bus en serie de alta velocidad. Las salidas con capacidad para drenaje abierto con resistores de desactivación internos optativos, con un control de tasa de velocidad de rotación configurable y una potencia de corriente programable, pueden transmitir hasta 16 mA para algunos estándares de la interfaz. -

Los bloques análogos que contienen ADC multicanal, un diodo de detección de temperatura y un oscilador en anillo de 116 MHz interno integrado terminan de completar esta poderosa arquitectura. Combinadas con convertidores delta-sigma o Modulación por ancho de pulsos (PWM) y el Generador DSP de Altera, puede usar las FPGA MAX 10 en el centro de las aplicaciones de monitoreo y control que requieren procesamiento de señal y conversión de ADC. Con la tecnología de memoria Flash NOR de 55 nm de TMSC, la rica colección de propiedad intelectual de Altera y un potente ecosistema de desarrollo, los diseñadores tienen acceso inmediato al tejido flexible de la FPGA del dispositivo. Este tejido incorpora bloques DSP, capacidad para interfaz LPDDR2/DDR3, PLL, hasta 50 K de elementos de lógica (LE) y 1.6 Mbits de RAM de bloque. En el centro de la cartera de IP de fácil uso de Altera se encuentra la herramienta de integración del sistema Qsys, que permite a los desarrolladores definir una arquitectura de sistema que crea una instancia de una amplia variedad de módulos de núcleo blando interoperables.

-

-

Figura 1 Entorno de desarrollo de Qsys (Ver más grande)

-

Esta cartera incluye el procesador integrado más versátil del mundo: el procesador Nios II de 32 bit. El procesador NIOS II puede operar a un máximo de 130 MHz para el núcleo rápido, una gran comunidad de usuarios y soporte integral para el sistema operativo.

Figura 2: Arquitectura del procesador Nios II y soporte del SO

Comience de inmediato con un kit de desarrollo

Los kits de desarrollo simplifican el proceso de diseño ya que permiten un desarrollo de diseño de FPGA rápido y software integrado en una plataforma de referencia bien documentada. Hay muchos kits disponibles y están optimizados para una amplia gama de aplicaciones. Basar una arquitectura de hardware subyacente en elementos de diseños de referencia probados le permite usar proyectos en marcha de ejemplo como punto de partida, lo cual agiliza el desarrollo y mitiga los riesgos. Acelere el tiempo de desarrollo mediante la combinación de esta estrategia con una amplia variedad de sistemas de operación disponibles con BSP específicos del kit de desarrollo, pilas de trabajo en red integradas y unidades de dispositivos.

El Kit de desarrollo integrado Nios II (NEEK) de Terasic tiene todo lo necesario para crear un sistema completo basado en procesador. Es una plataforma integrada con una cantidad de diseños de referencia que se enfocan en una gama de aplicaciones. El kit está optimizado para permitir el diseño rápido de soluciones personalizadas para aplicaciones de procesamiento integradas, productos de interfaz multimedia, interfaces hombre-máquina y visualización de videos. El kit presenta un panel capacitivo LCD, táctil, a color y multimedia con soporte nativo para múltiples gestos táctiles. También incorpora un sensor de imágenes de ocho megapíxeles, un sensor de luz y un acelerómetro de tres ejes. Los diseños de referencia para demostración incluyen control robótico, HDMI Rx, sensores, audio e interfaces de cámara.

Figura 3: Kit de desarrollo integrado MAX 10 Nios II de Terasic

El kit de desarrollo de FPGA MAX 10 de Altera está optimizado para una amplia variedad de aplicaciones que incluyen diseños de Ethernet industriales y HDMI. Hay disponibles diseños de referencia Linux integrados para el procesador Nios II. Además, presentan un sólido soporte de comunidad en línea. El kit de desarrollo incluye interfaces para incorporar tarjetas y periféricos con conectores HSMC y Digilent Pmod™ compatibles, asimismo cuenta con un control de alimentación de FPGA incorporado que usa la interfaz gráfica de usuario (GUI) del monitor de alimentación. El tablero está bien documentado, abierto y puede volver a usarse como plataforma probada en la cual basar un diseño.

Figura 4: Kit de desarrollo de FPGA MAX 10 de Altera

Figura 5: Arquitectura del kit de desarrollo de FPGA MAX 10 de Altera

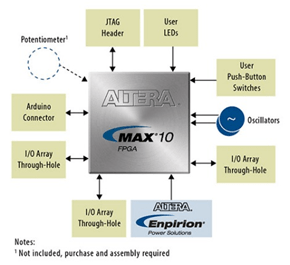

El Kit de evaluación de FPGA MAX 10 es un tablero básico de bajo costo con monitoreo de suministro de alimentación de FPGA integrado y una tensión de banco de E/S regulable para permitir la traslación de nivel. El tablero presenta un suministro de energía Enpiron de Altera y permite el acceso a la memoria Flash de la FPGA, a interfaces ADC y al anillo de E/S digital. El kit es increíblemente flexible como consecuencia de un conector de interfaz Arduino UNO R3 integrado que permite la conexión con blindajes Arduino compatibles. Esta característica admite miles de tableros periféricos con funcionalidades como sensores, controladores de motores, GPS y transceptores inalámbricos. El tablero PCB del kit y los esquemas están bien documentados y están disponibles como modelos para diseños.

Figura 6: Tablero de evaluación de FPGA MAX 10

Figura 7: Arquitectura del tablero de evaluación de FPGA MAX 10

El kit de desarrollo BeMicro MAX 10, disponible desde Arrow, permite a los diseñadores evaluar y utilizar la FPGA MAX 10 para aplicaciones integradas. Incluye un SoC Enpiron, 8 Mbytes de SDRAM, un acelerómetro, LED, botones y conectividad de expansión. Los cabezales de expansión incluyen dos conectores de 6 pines Digilent Pmod™ y dos cabezales de prototipo de 4 pines junto con un conector de borde de tarjeta de 80 pines. Los usuarios pueden interactuar directamente con las herramientas de desarrollo a través del puerto USB-Blaster incorporado. El tablero está bien documentado y cuenta con una Guía de introducción para el usuario (Getting Started User Guide) para acelerar los diseños, y es una perfecta plataforma de bajo costo para prototipos que permite un rápido desarrollo.

Figura 8: MAX 10 BeMicro

Figura 9: Arquitectura de MAX 10 BeMicro

El pequeño tablero de desarrollo DECA MAX 10 de Arrow es una plataforma de desarrollo potente, altamente versátil y resistente. Incorpora memoria DDR3, Ethernet, sensor de gestos con luz, HDMI TX, línea de entrada o salida de audio, enchufe microSD y dos entradas SMA para ADC MAX 10. El sistema DECA trae una cámara BYD y módulos de interfaz inalámbrica WiFi/BLE que se enchufan en los cabezales de expansión de 46 pines Beagle Bone Black (BBB). Los desarrolladores pueden usar el cabo compatible BeagleBone BLE/WIFI de Arrow que exhibe familias de soluciones BLE y WiFi de Texas Instruments. Los desarrolladores también pueden usar el módulo de la cámara para capturar imágenes CMOS de 8 megapíxeles con una interfaz de entrada de video MIPI.

Figura 10: Tablero de desarrollo de DECA MAX 10

Pruébelo hoy mismo

El desarrollo de un sistema sobre la base de una FPGA integrada nunca fue más sencillo. Las FPGA MAX 10 ofrecen niveles de integración que realmente permiten ahorros significativos en los costos. Una variedad de kits de desarrollo con soporte BSP para el sistema operativo y acceso a expansión periférica para sensores y conectividad en red habilitan las FPGA MAX 10 en aplicaciones que anteriormente requerían microcontroladores más complejos y costosos. La introducción de la carga flash de usuario y de la imagen dinámica a través de la interfaz UART con vigilancia y diseños con retroceso a prueba de fallas y con capacidad para mejoras en el futuro mediante la facilitación de las actualizaciones y el soporte. Los riesgos del desarrollo de hardware se reducen como consecuencia de soluciones resistentes bien documentadas y el software se acelera con diseños de referencia y una sólida comunidad de usuarios. Las herramientas de diseño de FPGA también incluyen opciones gratuitas basadas en la Web. El desarrollo de software y la depuración son sencillos con el entorno de desarrollo de software basado en Eclipse de Altera. Comuníquese con un representante de Altera para saber cómo puede comenzar hoy mismo.