전자 상거래, 원격 작업 및 클라우드 컴퓨팅과 같은 것들로의 지속적인 산업 마이그레이션으로 인해 데이터 센터에 대한 수요는 계속해서 기하급수적으로 증가하고 있습니다.

DDR4 표준 DRAM은 2014년에 채택된 이후로 광범위하게 채택되었습니다. 그러나 지난 몇 년간 신뢰성, 가용성 및 서비스 가능성에 대한 고객 요구가 증가함에 따라 차세대 DRAM이 필요하다는 사실이 분명해졌습니다. 최근 Micron Technology, Inc는 현재 사용 가능한 최신 DDR5 DRAM을 활용하는 차세대 컴퓨팅 플랫폼의 설계, 개발 및 검증을 지원하기 위해 포괄적인 TEP(Technology Enablement Program)를 발표했습니다.

2020년 1월, Micron은 DDR5 RDIMM 샘플 출시를 발표했습니다. 2020년 7월, JEDEC(전자 산업을 위한 글로벌 표준 기구)는 많은 사람들이 기대하는 JESD79-5 DDR5 SDRAM 표준을 발표했습니다. 새로운 DRAM의 기술에 대한 경험과 새로운 표준에 대한 참여로 인해 Micron, Cadence, Montage, Rambus, Renesas 및 Synopsys와 같은 회사는 시장 수요와 기술 개발의 결합에 존재합니다. TEP를 통해 이 비즈니스 그룹은 이 새로운 기술을 사용하여 신제품을 개발할 때 유통업체, 부가 가치 재판매자 및 OEM과 같은 채널 파트너와 협력하게 됩니다.

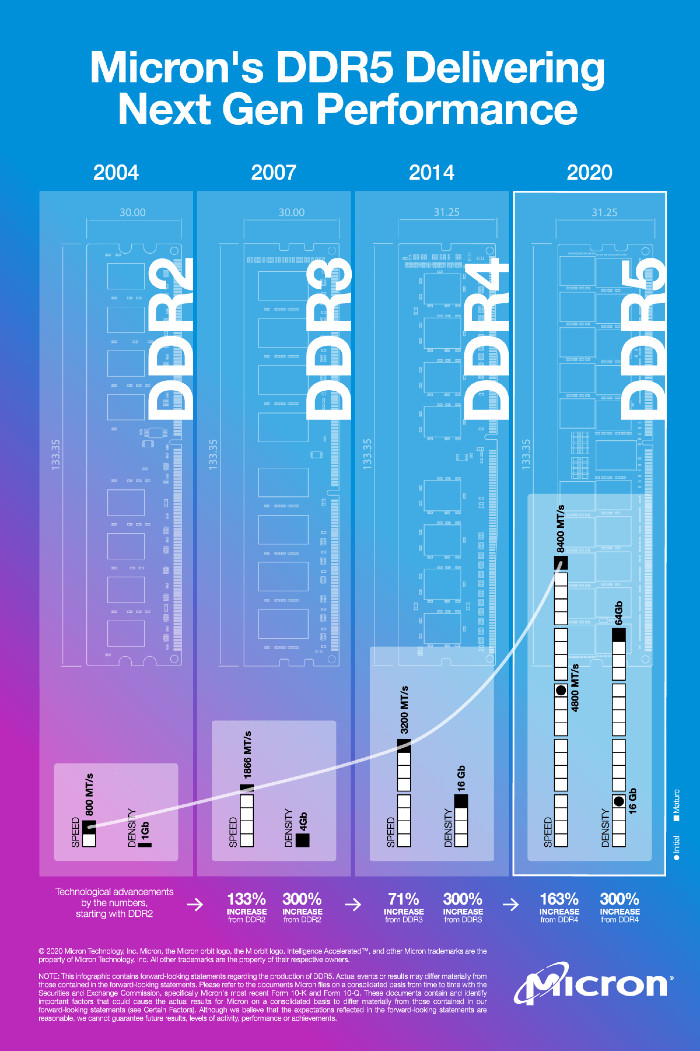

DDR5는 현재까지 기술적으로 가장 고급의 DRAM입니다. Micron의 업계 최고의 1znm 처리 기술로 구축된 DDR5는 85% 이상 향상된 메모리 성능을 제공합니다. 이러한 발전의 핵심은 메모리 밀도입니다. DDR5는 이전 DDR4 밀도의 두 배입니다. 이 인포그래픽에서 DRAM이 시간이 지남에 따라 속도가 기하급수적으로 빨라진 방법과 DDR5가 어떻게 지금까지 최고인지 알아보세요.

이러한 속도의 발전을 통해 프로세서 노심 수의 빠른 확장으로 최첨단 데이터 센터에 전력을 공급하는 데 필요한 메모리 광역폭과 용량의 증가가 가능합니다. 아래 표는 DDR5의 장점에 대한 개요를 제공합니다.

| 기능/의견 | DDR4 | DDR5 | DDR5 장점 | |||

| 데이터 정격 | 1600-3200MT/s | 3200-6400MT/s | 성능 및 광역폭 증가 | |||

| VDD/VDDQ/VPP | 1.2/1.2/2.5 | 1.1/1.1/1.8 | 전력 감소 | |||

| 내부 VREF | VREFDQ | VREFDQ, VREFCA, VREFCS | 전압 여유 개선, BOM 비용 절감 | |||

| 기기 밀도 | 2Gb-16Gb | 8Gb-64Gb | 더 큰 모놀리식 기기 사용 | |||

| 프리페치 | 8n | 16n | 내부 코어 클럭을 낮게 유지 | |||

| DQ 수신기 동등화 | CTLE | DFE | DRAM 내부에서 수신된 DQ 데이터 눈 열기 개선 | |||

| DCA(부하 주기 조절) | 없음 | DQS 및 DQ | 전송된 DQ/DQS 핀의 신호 처리 개선 | |||

| 내부 DQS 지연 모니터링 |

없음 | DQS 간격 진동자 | 환경 변화에 대한 견고성 향상 | |||

| 온다이 ECC | 없음 | 128b+8b SEC, 오류 검사 및 스크럽 | 온칩 RAS 강화 | |||

| CRC | 쓰기 | 읽기/쓰기 | 읽기 데이터를 보호하여 시스템 RAS 강화 | |||

| BG(뱅크 그룹)/뱅크 | 4BG x 4뱅크(x4/x8) 2BG x 4뱅크(x16) |

8BG x 2뱅크(8Gb x4/x8) 4BG x 2뱅크(8Gb x16) 8BG x 4뱅크(16-64Gb x4/x8) 4BG x 4뱅크(16-64Gb x16) |

광역폭/성능 개선 | |||

| 명령/주소 인터페이스 | ODT, CKE, ACT, RAS, CAS, WE, A |

CA<13:0> | CA 핀 수 대폭 감소 | |||

| ODT | DQ, DQS, DM/DBI | DQ, DQS, DM, CA 버스 | 신호 무결성 개선, BOM 비용 감소 | |||

| 파열 길이 | BL8(및 BL4) | BL16, BL32 (및 BC8 OTF, BL32 OTF) |

단 1개의 DIMM 하위 채널이 있는 64B 캐시 라인 페치를 허용합니다. | |||

| MIR(“미러” 핀) | 없음 | 예 | DIMM 신호 처리 개선 | |||

| 버스 반전 | DBI(데이터 버스 반전) | CAI(명령/주소 반전) | 모듈의 VDDQ 노이즈 감소 | |||

| CA 교육, CS 교육 | 없음 | CA 교육, CS 교육 | CA 및 CS 핀의 타이밍 마진 개선 | |||

| 레벨링 교육 모드 쓰기 | 예 | 개선됨 | 탁월한 DQ-DQS 경로에 대한 보상 | |||

| 교육 패턴 읽기 | MPR로 가능 | 직렬 전용 MR (사용자 정의), 클럭 및 LFSR 생성 교육 패턴 |

읽기 타이밍 마진을 더욱 강력하게 만듦 | |||

| 모드 레지스터 | 7x17비트 | 최대 256x8비트 (LPDDR 유형 읽기/쓰기) |

확장할 수 있는 공간 제공 | |||

| PRECHARGE 명령 | 모든 뱅크 및 뱅크당 | 모든 뱅크, 뱅크당 및 같은 뱅크 | PREsb는 각 BG에서 사전 충전 관련 뱅크 활성화 | |||

| REFRESH 명령 | 모든 뱅크 | 모든 뱅크 및 같은 뱅크 | REFsb는 각 BG에서 특정 뱅크를 리프레시할 수 있음 | |||

| 루프백 모드 | 없음 | 예 | DQ 및 DQS 신호 처리 테스트 활성화 |

Micron DDR5 TEP(기술 참여 프로그램) 이점:

승인된 파트너는 다음 대상에 액세스할 수 있습니다.

- 제품 개발 및 플랫폼 가져오기를 지원하는 데이터 시트, 전기, 열 및 시뮬레이션 모델과 같은 기술 리소스.

- 출시되었을 때 엄선된 DDR5 구성 요소 및 모듈 샘플.

- 설계를 지원하고 DDR5 지원 플랫폼을 가져올 수 있는 다른 에코 시스템 파트너와의 연결.

- 기술 지원 및 교육 자료.