随着行业不断向电子商务、远程工作和云计算等领域迁移,对数据中心的需求不断成倍增长。

DDR4 标准 DRAM 自 2014 年采用以来得到了广泛的应用。然而,在过去几年中,客户对可靠性、可用性和可维修性的要求不断提高,显然需要新一代 DRAM。近日,Micron Technology, Inc 宣布启动一项全面的技术赋能计划 (TEP),以帮助设计、开发和鉴定采用目前最先进的 DDR5 DRAM 的下一代计算平台。

2020 年 1 月,Micron 宣布推出 DDR5 RDIMM 样品。2020 年 7 月,JEDEC(全球电子行业标准组织)发布了广受关注的 JESD79-5 DDR5 SDRAM 标准。由于 Micron、Cadence、Montage、Rambus、Renesas 和 Synopsys 等公司在全新 DRAM 的技术细节方面拥有丰富的经验,并参与了新标准的制定,因此它们处于市场需求与技术发展的联结点。通过 TEP,这批企业将与分销商、增值经销商和 OEM 等渠道合作伙伴携手,利用这一新技术开发新产品。

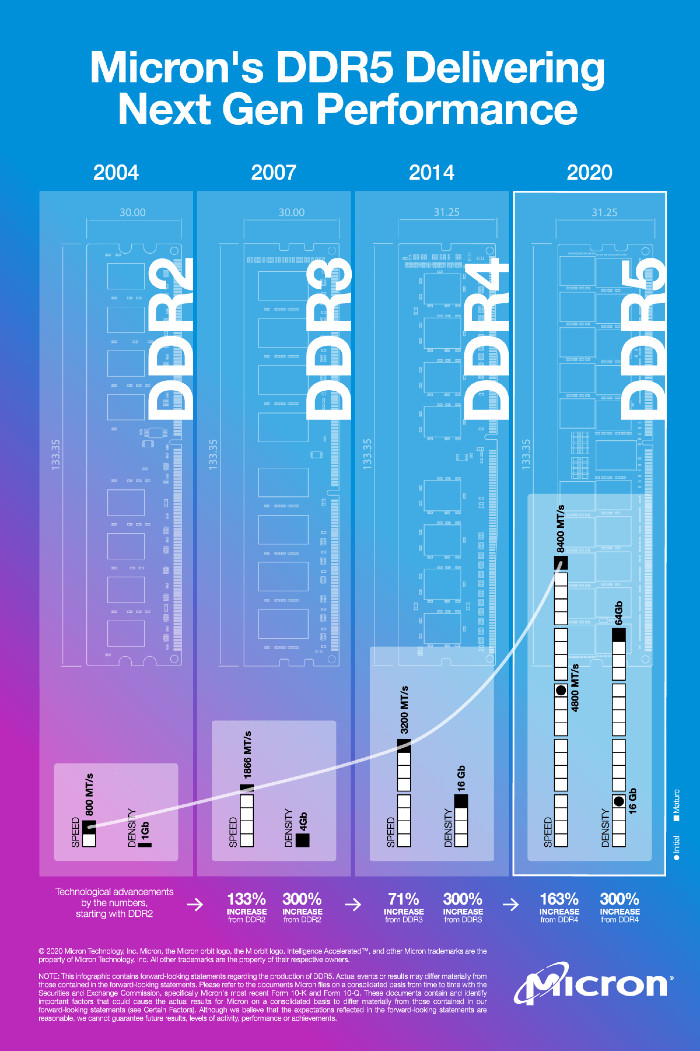

DDR5 是迄今为止技术最先进的 DRAM。DDR5 采用 Micron 业界领先的 1znm 工艺技术,使内存性能提高了 85% 以上。这一进步的关键在于内存密度 - DDR5 的内存密度是其前身 DDR4 的两倍。在这张信息图中,我们可以看到 DRAM 如何随着时间的推移令速度呈指数级增长,以及 DDR5 如何做到最好。

这种速度上的演进允许增加内存带宽和容量,以便为处理器核心数量快速扩展的尖端数据中心提供动力。下表概述了 DDR5 的优势:

| 特性/特点 | DDR4 | DDR5 | DDR5 优势 | |||

| 数据传输率 | 1600-3200 MT/s | 3200-6400 MT/s | 提高性能和带宽 | |||

| VDD/VDDQ/VPP | 1.2/1.2/2.5 | 1.1/1.1/1.8 | 降低功率 | |||

| 内部 VREF | VREFDQ | VREFDQ、VREFCA、VREFCS | 提高电压裕量,降低物料清单成本 | |||

| 设备密度 | 2Gb-16Gb | 8Gb-64Gb | 支持更大的单片器件 | |||

| 预读取 | 8n | 16n | 保持内部内核时钟低电平 | |||

| DQ 接收器等化 | CTLE | DFE | 改善 DRAM 内部接收到的 DQ 数据眼的打开情况 | |||

| 占空比调整 (DCA) | 无 | DQS 和 DQ | 改善传输的 DQ/DQS 引脚上的信号传送 | |||

| 内部 DQS 延迟 监控 |

无 | DQS 间歇振荡器 | 增强对环境变化的鲁棒性 | |||

| 片上 ECC | 无 | 128b+8b SEC,错误检查和清除 | 增强片上 RAS | |||

| CRC | 写入 | 读取/写入 | 通过保护读取数据增强系统 RAS | |||

| 数据组 (BG)/存储体 | 4 BG x 4 存储体 (x4/x8) 2 BG x 4 存储体 (x16) |

8 BG x 2 存储体 (8Gb x4/x8) 4 BG x 2 存储体 (8Gb x16) 8 BG x 4 存储体 (16-64Gb x4/x8) 4 BG x 4 存储体 (16-64Gb x16) |

提高带宽/性能 | |||

| 命令/地址接口 | ODT、CKE、ACT、RAS、 CAS、WE、A |

CA<13:0> | 大幅减少 CA 引脚数量 | |||

| ODT | DQ、DQS、DM/DBI | DQ、DQS、DM、CA 总线 | 提高信号完整性,降低物料清单成本 | |||

| 脉冲时间 | BL8(和 BL4) | BL16、BL32 (和 BC8 OTF、BL32 OTF) |

只需 1 个 DIMM 子通道,即可获得 64B 高速缓存行读取。 | |||

| MIR(“镜像”引脚) | 无 | 是 | 改善 DIMM 信号传送 | |||

| 总线倒置 | 数据总线倒置 (DBI) | 命令/地址倒置 (CAI) | 降低模块上的 VDDQ 噪声 | |||

| CA 调驯,CS 调驯 | 无 | CA 调驯,CS 调驯 | 提高 CA 和 CS 引脚的时序裕量 | |||

| 写入均衡调驯模式 | 是 | 改善 | 补偿不匹配的 DQ-DQS 路径 | |||

| 读取调驯模式 | 可通过 MPR 实现 | 串行专用 MR (由用户定义)、时钟和 LFSR -生成的调驯模式 |

使读取时序裕量更加稳定 | |||

| 模式寄存器 | 7 x 17 位 | 最高 256 x 8 位 (LPDDR 类型读/写) |

提供扩展空间 | |||

| 预充电命令 | 所有存储体和每个存储体 | 所有存储体,每个存储体,以及同一存储体 | PREsb 支持每个 BG 中的特定存储体预充电 | |||

| 刷新命令 | 所有存储体 | 所有存储体和同一存储体 | REFsb 支持每个 BG 中的特定存储体刷新 | |||

| 环回模式 | 无 | 是 | 支持 DQ 和 DQS 信号传送测试 |

Micron DDR5 技术参与计划 (TEP) 优势:

经批准的合作伙伴可获得:

- 技术资源,如数据表、电气、热力和模拟模型,以帮助产品开发和平台启动。

- 选择可用的 DDR5 组件和模块样品。

- 与其他生态系统合作伙伴的联系,这有助于设计和启动支持 DDR5 的平台。

- 技术支持和培训材料。