Avec la migration continue de l'industrie vers le commerce électronique, le télétravail ou le cloud, la sollicitation des centres de données croît de manière exponentielle.

La mémoire DRAM de type DDR4 a été largement adoptée depuis son apparition en 2014. Toutefois, l'élévation du niveau d'exigence des clients en matière de fiabilité, de disponibilité et de facilité d'entretien de ces dernières années montre qu'une nouvelle génération de DRAM est nécessaire. Récemment, Micron Technology, Inc a annoncé un programme d'habilitation technologique (TEP, Technology Enablement Program) destiné à aider à la conception, au développement et à la qualification de plateformes informatiques de nouvelle génération utilisant la DRAM DDR5, la norme la plus avancée à l'heure actuelle.

En janvier 2020, Micron a annoncé le déploiement de prototypes de RDIMM DDR5. En juillet 2020, la JEDEC (l'organisation de normalisation internationale pour le secteur de l'électronique) a publié sa norme très attendue de SDRAM DDR5 JESD79-5. Fortes de leur expérience avec les particularités techniques de la nouvelle DRAM et de leur engagement vis-à-vis des nouvelles normes, des sociétés comme Micron, Cadence, Montage, Rambus, Renesas et Synopsys se trouvent au cœur des exigences du marché et du développement technique. Avec le TEP, ces entreprises travailleront main dans la main avec des partenaires comme des distributeurs, des revendeurs à valeur ajoutée (VAR) et des OEM au développement de nouveaux produits utilisant cette nouvelle technologie.

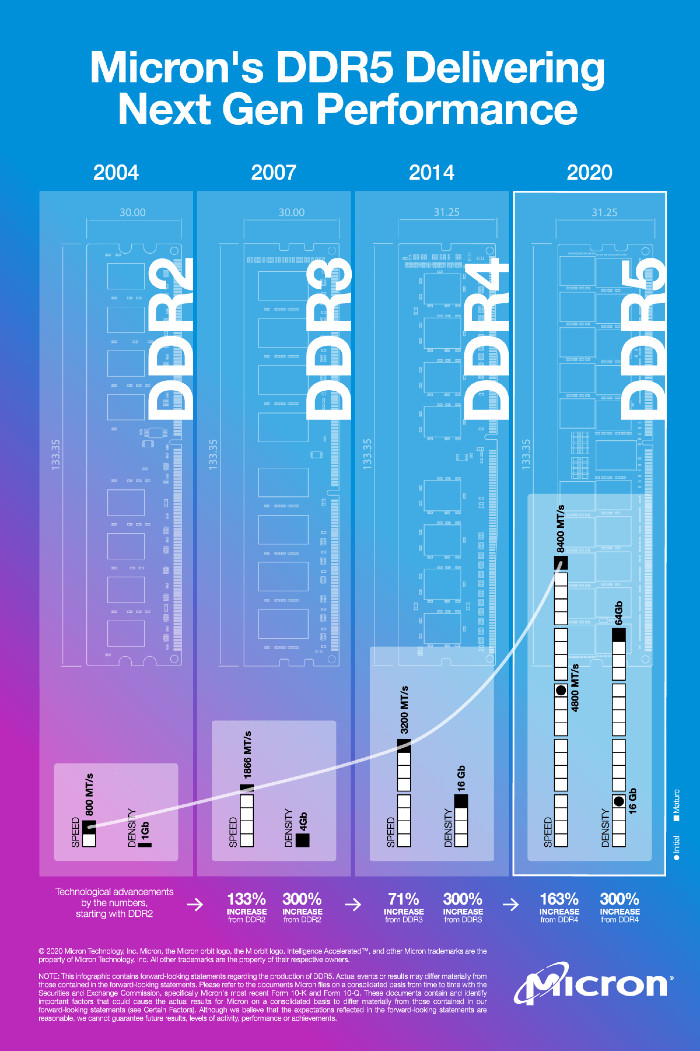

DDR5 est la DRAM la plus technologiquement avancée à ce jour. Bâtie sur la technologie de traitement 1znm leader du secteur de Micron, la DDR5 produit plus de 85 % d'augmentation des performances de mémoire. La clé de ce progrès est la densité de la mémoire - la spécification DDR5 en a deux fois plus que sa prédécesseure DDR4. Dans cette infographie, vous pouvez voir les augmentations exponentielles de la DRAM dans le temps, jusqu'à la DDR5.

Cette évolution de la vitesse permet l'utilisation de la bande passante et des capacités nécessaires pour alimenter les centres de données de pointe avec toujours plus de cœurs de processeur. Le tableau ci-dessous offre une vue d'ensemble des avantages de la DDR5 :

| Fonctionnalité/Opinion | DDR4 | DDR5 | Avantages de la DDR5 | |||

| Débits de données | 1 600 - 3 200 MT/s | 3 200 - 6 400 MT/s | Améliore les performances et la bande passante | |||

| VDD/VDDQ/VPP | 1.2/1.2/2.5 | 1.1/1.1/1.8 | Réduit la puissance | |||

| VREF interne | VREFDQ | VREFDQ, VREFCA, VREFCS | Améliore les marges de tension, réduit les coûts de nomenclature | |||

| Densités des appareils | 2 Go - 16 Go | 8 Go - 64 Go | Autorise les appareils monolithiques de plus grande taille | |||

| Prélecture | 8 n | 16 n | Maintient l'horloge interne du cœur basse | |||

| Égalisation du récepteur DQ | CTLE | DFE | Améliore l'ouverture des données DQ reçues dans la DRAM | |||

| Réglage du cycle de service (DCA) | Aucun(e) | DQS et DQ | Améliore la signalisation sur les broches DQ/DQS transmises | |||

| Surveillance de délai DQS interne |

Aucun(e) | Oscillateur d'intervalle DQS | Améliore la robustesse face aux bouleversements climatiques | |||

| CCE intégrée | Aucun(e) | SEC 128b+8b, détection et correction d'erreurs | Renforce RAS sur puce | |||

| CRC | Écriture | Lecture/écriture | Renforce la RAS système en protégeant les données de lecture | |||

| Groupes banques (BG)/Banques | 4 BG x 4 banques (x4/x8) 2 BG x 4 banques (x16) |

8 BG x 2 banques (8 Go x4/x8) 4 BG x 2 banques (8 Go x16) 8 BG x 4 banques (16-64 Go x4/x8) 4 BG x 4 banques (16-64 Go x16) |

Améliore la bande passante/performance | |||

| Interface commande/adresse | ODT, CKE, ACT, RAS, CAS, WE, A |

CA<13:0> | Réduit significativement le nombre de broches CA | |||

| ODT | DQ, DQS, DM/DBI | DQ, DQS, DM, bus CA | Améliore l'intégrité du signal, réduit les coûts de nomenclature | |||

| Longueur de rupture (BL) | BL8 (et BL4) | BL16, BL32 (et BC8 OTF, BL32 OTF) |

Autorise lecture de ligne cache 64B avec 1 sous-canal DIMM uniquement. | |||

| MIR (broche « miroir ») | Aucun(e) | Oui | Améliore signalisation DIMM | |||

| Inversion de bus | Inversion de bus de données (DBI) | Inversion commande/adresse (CAI) | Réduit bruit VDDQ sur modules | |||

| Formation CA, formation CS | Aucun(e) | Formation CA, formation CS | Améliore marge de synchronisation sur broches CA et CS | |||

| Modes de formation niveau écriture | Oui | Améliorés | Compense pour chemin DQ-DQS sans équivalent | |||

| Schémas de formation à la lecture | Possible avec le MPR | MR dédiés pour schémas de formation générés par série (défini par utilisateur), horloge et LFSR |

Renforce marge de synchronisation de lecture | |||

| Registres de modes | 7 x 17 bits | Jusqu'à 256 x 8 bits (lecture/écriture de type LPDDR) |

Fournit espace d'expansion | |||

| Commandes PRECHARGE | Toutes les banques et par banque | Toutes les banques, par banque et même banque | PREsb permet le préchargement d'une banque donnée dans chaque BG | |||

| Commandes REFRESH | Toutes les banques | Toutes les banques et même banque | REFsb permet le rafraîchissement d'une banque donnée dans chaque BG | |||

| Mode rebouclage | Aucun(e) | Oui | Permet le test de la signalisation DQ et DQS |

Avantages du TEP (programme d'habilitation technologique) DDR5 Micron :

Les partenaires agréés peuvent accéder à :

- Des ressources techniques telles que les fiches techniques, les modèles électriques, thermiques et de simulation qui aident au développement du produit et à la création de plateforme.

- Échantillons de composants et de modules DDR5 à mesure qu'ils sont disponibles.

- Contact avec autres partenaires de l'écosystème susceptibles d'aider à la conception et à l'élaboration de plateformes DDR5.

- Support technique et éléments de formation.

Télécharger le communiqué de presse