業界が電子商取引、リモートワーク、クラウド コンピューティングなどに移行し続けるにつれて、データ センターに対する需要は飛躍的に増加し続けています。

DDR4規格のDRAMは、2014年に採用されて以来、広く採用されてきました。しかし、ここ数年で信頼性、可用性、保守性に対する顧客の要求が高まり、新世代のDRAMが必要であることが明らかになりました。最近、 Micron Technology, Inc は、現在利用可能な最も先進的なDDR5 DRAMを活用した次世代コンピューティング プラットフォームの設計、開発、認定を支援する包括的なテクノロジー イネーブルメント プログラム (TEP) を発表しました。

2020年1月、MicronはDDR5 RDIMMサンプルの展開を発表しました。2020年7月、JEDEC (電子業界の世界標準化団体) は、広く期待されていたJESD79-5 DDR5 SDRAM規格を公開しました。Micron、Cadence、Montage、Rambus、Renesas、Synopsysなどの企業は、新しいDRAMの技術的経験と新しい標準への取り組みにより、市場の需要と技術開発の結節点に存在しています。TEPにより、この企業グループは、ディストリビューター、付加価値再販業者、OEMなどのチャネル パートナーと連携して、この新しいテクノロジーを使用して新製品を開発します。

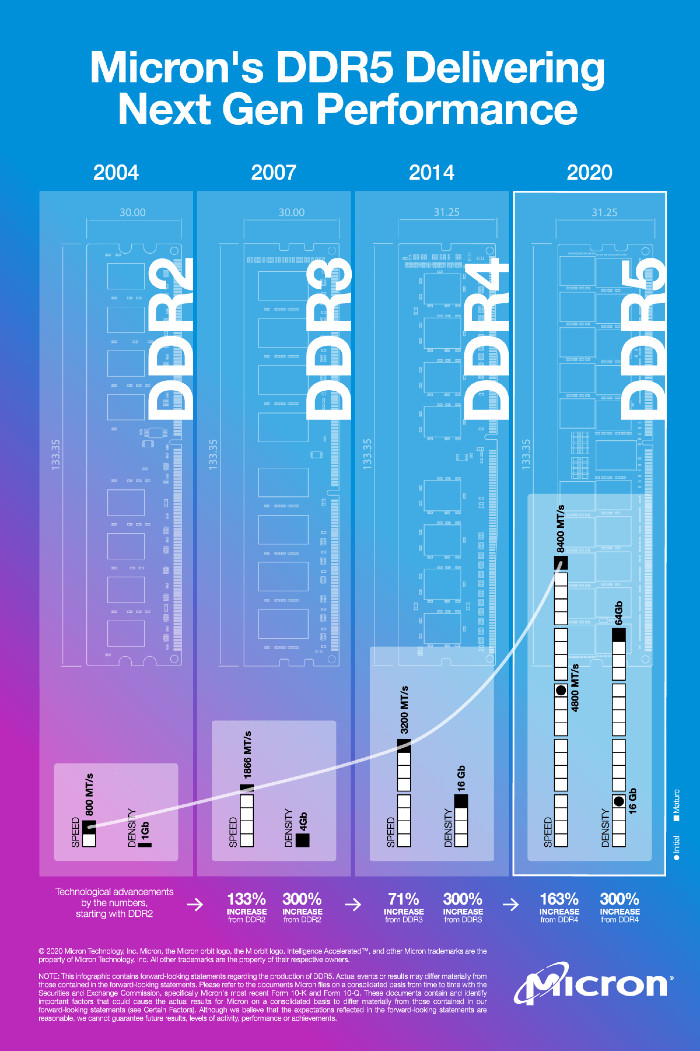

DDR5は、現在までに最も技術的に進歩したDRAMです。Micronの業界をリードする1znmプロセス テクノロジーに基づいて構築されたDDR5は、メモリ パフォーマンスを85% 以上向上させます。この進歩の鍵となるのはメモリ密度です。DDR5は前身のDDR4の2倍の密度を備えています。このインフォグラフィックでは、DRAMの速度が時間の経過とともにどのように飛躍的に向上してきたか、そしてDDR5がこれまでで最高である理由について説明します。

この速度の進化により、急速に増加するプロセッサ コア数に対応する最先端のデータ センターに必要なメモリ帯域幅と容量が増大します。以下の表は、DDR5の利点の概要を示しています。

| 特集/意見 | DDR4 | DDR5 | DDR5の利点 | |||

| データレート | 1600-3200 MT/秒 | 3200-6400 MT/秒 | パフォーマンスと帯域幅を向上 | |||

| 五DD /V DDQ /V PP | 1.2/1.2/2.5 | 1.1/1.1/1.8 | パワーを下げる | |||

| 内部VREF | 五参照 | 五参照、V REFCA、V参照 | 電圧マージンを改善し、BOMコストを削減 | |||

| デバイス密度 | 2Gb-16Gb | 8Gb-64Gb | より大きなモノリシックデバイスを実現 | |||

| プリフェッチ | 8n | 16n | 内部コアクロックを低く保つ | |||

| DQ受信機イコライゼーション | CTLE | ドイツ連邦共和国 | DRAM内の受信DQデータアイの開きを改善 | |||

| デューティサイクル調整(DCA) | なし | DQSとDQ | 送信されたDQ/DQSピンの信号を改善します | |||

| 内部DQS遅延 監視 |

なし | DQSインターバルオシレータ | 環境変化に対する堅牢性の向上 | |||

| オンダイECC | なし | 128b+8b SEC、エラーチェックおよびスクラブ | オンチップRASを強化 | |||

| CRCP | 書く | 読み取り/書き込み | 読み取りデータを保護することでシステムRASを強化 | |||

| 銀行グループ(BG)/銀行 | 4 BG x 4バンク (x4/x8) 2 BG x 4バンク (x16) |

8 BG x 2バンク (8Gb x4/x8) 4 BG x 2バンク (8Gb x16) 8 BG x 4バンク (16-64Gb x4/x8) 4 BG x 4バンク (16-64Gb x16) |

帯域幅/パフォーマンスの向上 | |||

| コマンド/アドレスインターフェース | ODT、CKE、ACT、RAS、CAS、WE、A<X:0> |

CA<13:0> | CAピン数を大幅に削減 | |||

| ODTAの | DQ、DQS、DM/DBI | DQ、DQS、DM、CAバス | 信号の整合性を改善し、BOMコストを削減 | |||

| バースト長 | BL8 (およびBL4) | BL16、BL32 (およびBC8 OTF、BL32 OTF) |

1つのDIMMサブチャネルのみで64Bキャッシュ ライン フェッチが可能になります。 | |||

| MIR(「ミラー」ピン) | なし | はい | DIMMシグナリングの改善 | |||

| バス反転 | データバス反転 (DBI) | コマンド/アドレス反転 (CAI) | モジュールのVDDQノイズを低減 | |||

| CA研修、CS研修 | なし | CA研修、CS研修 | CAピンとCSピンのタイミングマージンを改善 | |||

| レベルアップトレーニングモードを書く | はい | 改善された | 不一致のDQ-DQSパスを補正 | |||

| トレーニングパターンを読む | MPRで可能 | シリアル (ユーザー定義)、クロック、LFSR 生成のトレーニング パターン専用のMR |

読み取りタイミングマージンをより堅牢にする | |||

| モードレジスタ | 7 x 17ビット | 最大256 x 8ビット (LPDDRタイプ読み取り/書き込み) |

拡張の余地を提供 | |||

| PRECHARGEコマンド | 全銀行および銀行ごと | すべての銀行、銀行ごと、同じ銀行 | PREsbは各BGの特定のバンクのプリチャージを可能にします | |||

| REFRESHコマンド | すべての銀行 | すべての銀行および同じ銀行 | REFsbは各BG内の特定のバンクのリフレッシュを可能にする | |||

| ループバックモード | なし | はい | DQおよびDQS信号のテストが可能 |

Micron DDR5テクニカルエンゲージメントプログラム (TEP) のメリット:

承認されたパートナーは、次のものにアクセスできます:

- 製品開発とプラットフォームの立ち上げに役立つデータシート、電気、熱、シミュレーション モデルなどの技術リソース。

- DDR5コンポーネントおよびモジュールのサンプルが利用可能になったら選択します。

- DDR5対応プラットフォームの設計と構築を支援できる他のエコシステム パートナーとのつながり。

- 技術サポートとトレーニング資料。