Con la continua migrazione verso l'e-commerce, il telelavoro e il cloud computing, la richiesta di datacenter sta crescendo in modo esponenziale.

L'utilizzo della memoria DRAM di tipo DDR4 si è ampiamente diffuso dalla prima adozione nel 2014. Tuttavia, l'aumento della richiesta di affidabilità, disponibilità e funzionalità da parte dei clienti negli ultimi anni indica che è necessaria una nuova generazione di DRAM. Di recente, Micron Technology, Inc ha annunciato un programma completo di attivazione della tecnologia (TEP, Technology Enablement Program) per aiutare a progettare, sviluppare e qualificare piattaforme di elaborazione di nuova generazione basate su DRAM DDR5, lo standard più avanzato disponibile oggi.

Nel gennaio 2020, Micron ha annunciato lo sviluppo dei modelli RDIMM DDR5. Nel luglio 2020, JEDEC, l'organizzazione mondiale che si occupa dello sviluppo di standard per l'industria elettronica, ha rilasciato lo standard ampiamente atteso JESD79-5 DDR5 SDRAM. Forti della loro esperienza con gli aspetti tecnici della nuova DRAM e del loro impegno con i nuovi standard, aziende come Micron, Cadence, Montage, Rambus, Renesas e Synopsys sono al centro delle esigenze del mercato e dello sviluppo tecnico. Con il TEP, questo gruppo di aziende lavorerà mano nella mano con partner di canale come distributori, rivenditori a valore aggiunto e OEM per sviluppare nuovi prodotti utilizzando questa nuova tecnologia.

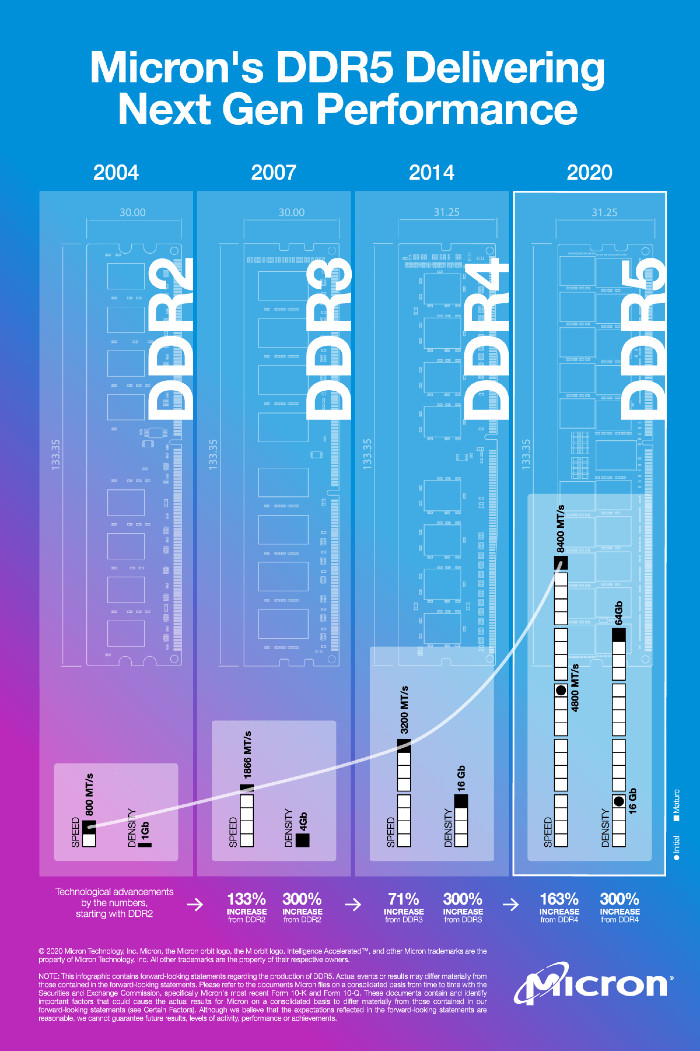

La DDR5 è la DRAM tecnologicamente più avanzata fino ad oggi. Basata sulla tecnologia di elaborazione 1znm leader del settore di Micron, la DDR5 offre prestazioni di memoria superiori dell'85%. La chiave di questo progresso è la densità di memoria: la DDR5 ne ha il doppio rispetto alla precedente DDR4. In questa infografica è possibile vedere gli aumenti esponenziali di velocità della DRAM nel tempo e come la DDR5 sia ancora la migliore.

Questa evoluzione della velocità consente di utilizzare capacità e ampiezza di banda della memoria maggiori per alimentare datacenter all'avanguardia con un numero sempre maggiore di core processori. Nella tabella che segue viene fornita una panoramica dei vantaggi della DDR5:

| Caratteristica/Opinione | DDR4 | DDR5 | Vantaggio della DDR5 | |||

| Velocità dei dati | 1600-3200 MT/s | 3200-6400 MT/s | Incrementa prestazioni e ampiezza di banda | |||

| VDD/VDDQ/VPP | 1.2/1.2/2.5 | 1.1/1.1/1.8 | Riduce i consumi | |||

| VREF interno | VREFDQ | VREFDQ, VREFCA, VREFCS | Migliora i margini di tensione, riduce i costi della distinta base | |||

| Densità di potenza del dispositivo | 2 Gb - 16 Gb | 8 Gb - 64 Gb | Consente dispositivi monolitici più grandi | |||

| Pre-recupero | 8 n | 16 n | Mantiene basso il clock del core interno | |||

| Equalizzazione del ricevitore DQ | CTLE | DFE | Migliora l'apertura dei dati DQ ricevuti nella DRAM | |||

| Regolazione del ciclo di servizio (DCA) | Nessuno | DQS e DQ | Migliora la segnalazione sui pin DQ/DQS trasmessi | |||

| Monitoraggio ritardo DQS interno |

Nessuno | Oscillatore intervallo DQS | Incrementa la robustezza contro i cambiamenti climatici | |||

| ECC su die | Nessuno | SEC 128b+8b, controllo e correzione di errori | Rafforza RAS su chip | |||

| CRC | Scrittura | Lettura/Scrittura | Rafforza RAS sistema tramite protezione dei dati in lettura | |||

| Gruppi di banchi (BG)/banchi | 4 BG x 4 banchi (x4/x8) 2 BG x 4 banchi (x16) |

8 BG x 2 banchi (8 Gb x4/x8) 4 BG x 2 banchi (8 Gb x16) 8 BG x 4 banchi (16-64 Gb x4/x8) 4 BG x 4 banchi (16-64 Gb x16) |

Migliora ampiezza di banda/prestazioni | |||

| Interfaccia di comando/indirizzo | ODT, CKE, ACT, RAS, CAS, WE, A |

CA<13:0> | Riduce drasticamente il numero di pin CA | |||

| ODT | DQ, DQS, DM/DBI | DQ, DQS, DM, bus CA | Migliora l'integrità di segnale, riduce i costi della distinta base | |||

| Lunghezza di rottura | BL8 (e BL4) | BL16, BL32 (e BC8 OTF, BL32 OTF) |

Consente il recupero della riga della cache da 64 B con 1 solo sottocanale DIMM. | |||

| MIR (pin "specchio") | Nessuno | Sì | Migliora la segnalazione DIMM | |||

| Inversione del bus | Inversione del bus di dati (DBI) | Inversione di comando/indirizzo (CAI) | Riduce rumore VDDQ su moduli | |||

| Formazione CA, formazione CS | Nessuno | Formazione CA, formazione CS | Migliora margini di temporizzazione su pin CA e CS | |||

| Modalità di formazione livello di scrittura | Sì | Migliorato | Compensa il percorso DQ-DQS senza pari | |||

| Modelli di formazione lettura | Possibile con MPR | MR dedicati per modelli di formazione generati da serie (definiti dall'utente), clock ed LFSR |

Rafforza il margine di sincronizzazione della lettura | |||

| Registri modalità | 7 x 17 bit | Fino a 256 x 8 bit (lettura/scrittura di tipo LPDDR) |

Fornisce spazio di espansione | |||

| Comandi PRECHARGE | Tutti i banchi e per banco | Tutti i banchi, per banco e stesso banco | PREsb consente il precaricamento di un banco specifico in ogni BG | |||

| Comandi REFRESH | Tutti i banchi | Tutti i banchi e stesso banco | REFsb consente l'aggiornamento di un banco specifico in ogni BG | |||

| Modalità loopback | Nessuno | Sì | Consente il test di segnalazione DQ e DQS |

Vantaggi del programma TEP (Technical Engagement Program) DDR5 di Micron:

I partener approvati possono accedere a:

- Risorse tecniche come schede tecniche, modelli elettrici, termici e di simulazione per assistere nello sviluppo del prodotto e nella messa in servizio della piattaforma.

- Selezione di campioni di componenti e moduli DDR5 non appena sono disponibili.

- Connessione con altri partner dell'ecosistema che possono aiutare nella progettazione e nella messa in servizio di piattaforme abilitate alla DDR5.

- Supporto tecnico e materiale di formazione.